Clock Reset Generator (CRG)

Introduction

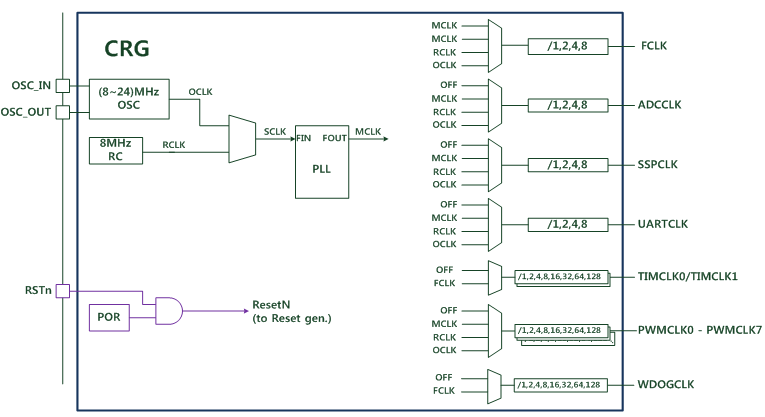

CRG is clock reset generator block for W7500 System. It provides every clock/reset for all other block include CPU and peripherals. CRG includes PLL and POR.

Features

Reset

- Three type of reset – external reset, Power reset, system reset

- External reset is generated by low level on the RSTn pin (external reset)

- Power reset is generated by Power-on reset (POR)

- Power on reset is generated by POR

- System reset is generated when one of the following events occurs

- Watchdog event

- After remapping

- Software reset (SYSRESETREQ bis in Cortex-M0. Refer to the Cortex-M0 technical reference manual for more detail)

- Power reset sets all registers to their reset values

- System reset sets all registers to their reset values except the CRG block registers and remap register to protect remap value

Clock

Two clock sources can be used to drive the system clock.

- External oscillator clock (8MHz ~ 24MHz) (OCLK)

- Internal 8MHz RC oscillator clock (RCLK)

One additional clock source

- 32.768KHz low speed external crystal which derives the real time clock.

There is a PLL One PLL is integrated

- Input clock range is from 8MHz to 24MHz

- Frequency can be generated by M/N/OD registers. (refer register description)

- Bypass option enabled

There are many generated clocks for independent operating with system clock

- System clock (FCLK)

- ADC clock (ADCCLK)

- SSP0, SSP1 clock (SSPCLK)

- UART0, UART1 clock (UARTCLK)

- Two Timer clocks (TIMCLK0, TIMCLK1)

- 8ea PWM clocks (PWMCLK0 - PWMCLK7)

- Real time clock (RTCCLK)

- WDOG clock (WDOGCLK)

- Random number generator clock (RNGCLK)

RNGCLK have only one source (pll output) and no prescaler Some of the generated clocks turn off automatically when CPU enters sleep mode.

- ADCCLK, RNGCLK

Generate two Hardware TCPIP Clocks (MII_RXC, MII_TXC) are from external PADs.

Hardware TCPIP Clocks can be gated by register control.

All clocks generated from CRG can be monitored.

Functional description

External Oscillator Clock

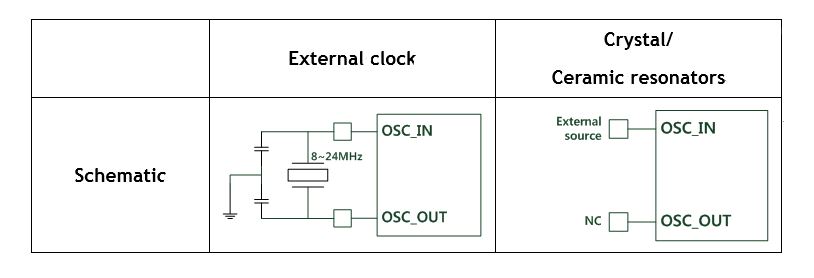

External oscillator clock (OCLK) can be generated from two possible clock source

- External crystal/ceramic resonator (8 to 24MHz external oscillator)

- User external clock

RC oscillator clock

RC oscillator clock (RCLK) signal is generated from an internal 8MHz RC oscillator.

RC oscillator has the advantage of providing a clock source at low cost (no external components).

However accuracy of RC oscillator is less than external crystal or ceramic resonator.

PLL

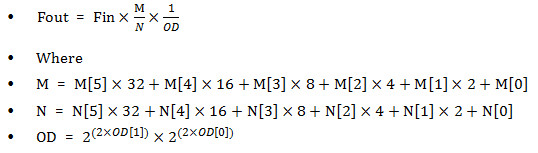

The internal PLL can be used to multiply the External Oscillator Clock (OCLK) or RC Oscillator Clock (RCLK). PLL input can be selected by register. PLL output clock can be generated by following the equations below.

Generated clock

Each generated clock source can be selected among 3 clock source as independent by each clock source select register

- PLL output clock (MCLK)

- Internal 8MHz RC oscillator clock (RCLK)

- External oscillator clock (8MHz ~ 24MHz) (OCLK)

Each generated clock has own prescaler which can be select individually by each prescale value register

- FCLK, ADCCLK, SSPCLK, UARTCLK : 1/1, 1/2, 1/4, 1/8

- TIMCLK0, TIMCLK1, PWMCLK0 – PWMCLK7, WDOGCLK : 1/1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128