WIZ810SMJ

WIZ810SMJ

The WIZ810SMJ is a versatile Ethernet module based on the W5100S hardwired TCP/IP chip with integrated PHY and RJ45 (MAG-JACK).

It supports both SPI and Parallel System Bus interfaces, allowing flexible connectivity options for embedded network systems.

With full hardware TCP/IP stack offload and minimal design effort, it is an ideal choice for rapid Ethernet integration.

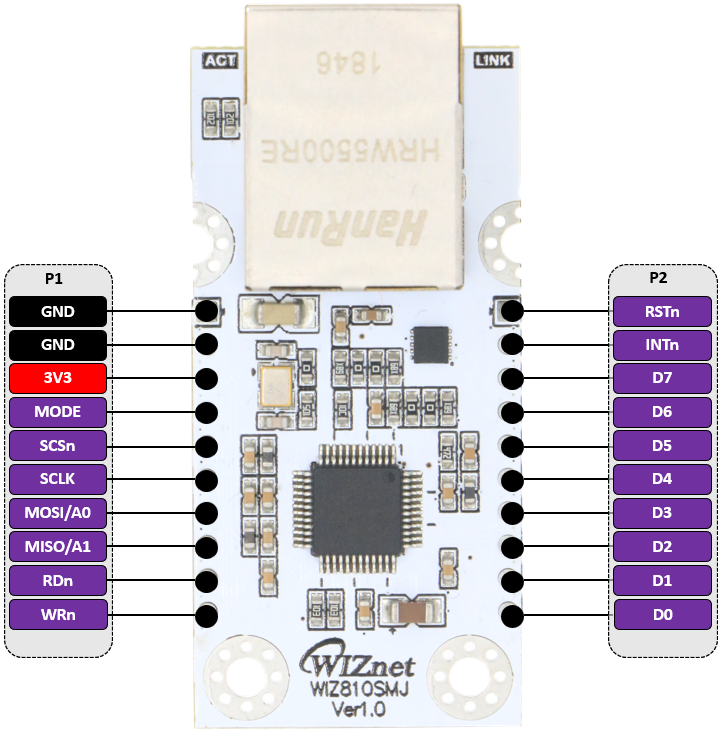

Pin Information

- All Pins

P1

| Pin | Type | Name | Description |

|---|---|---|---|

| 1 | P | GND | Ground |

| 2 | P | INTn | Interrupt output (active low) |

| 3 | P | 3V3D | 3.3 V Power |

| 4 | I | MODE | SPI/BUS Select pin SPI : Low BUS : High |

| 5 | I | SCSn | SPI Chip select (active low) |

| 6 | I | SCLK | SPI Clock input |

| 7 | I | MOSI/A0 | SPI : Master-Out / Slave-In BUS : A0 |

| 8 | O/I | MISO/A1 | SPI : Master-In / Slave-Out BUS : A1 |

| 9 | I | RDn | Read Strobe SPI : indicates Read Operation BUS : indicates Read Operation |

| 10 | I | WRn | Write Strobe SPI : indicates Read Operation BUS : indicates Write Operation |

P2

| Pin | Type | Name | Description |

|---|---|---|---|

| 1 | I | RSTn | Hardware reset (active low, ≥ 1 µs) |

| 2 | O | INTn | Interrupt output (low-active) |

| 3 | IO | D7 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W5100S |

| 4 | IO | D6 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W5100S |

| 5 | IO | D5 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W5100S |

| 6 | IO | D4 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W5100S |

| 7 | IO | D3 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W5100S |

| 8 | IO | D2 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W5100S |

| 9 | IO | D1 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W5100S |

| 10 | IO | D0 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W5100S |

Features

- Supports Hardwired TCP/IP protocols: TCP, UDP, ICMP, IGMPv1/v2, IPv4, ARP, PPPoE

- 4 independent sockets for simultaneous connections

- Supports Wake-on-LAN (UDP) and SOCKET-less commands (ARP, PING)

- High-speed SPI and Parallel Bus Interface (2 address, 8-bit data)

- Integrated transformer and RJ45 (MAG-JACK)

- Auto-Negotiation and Auto-MDIX (10/100 Mbps)

- Power-down and clock gating for low power operation

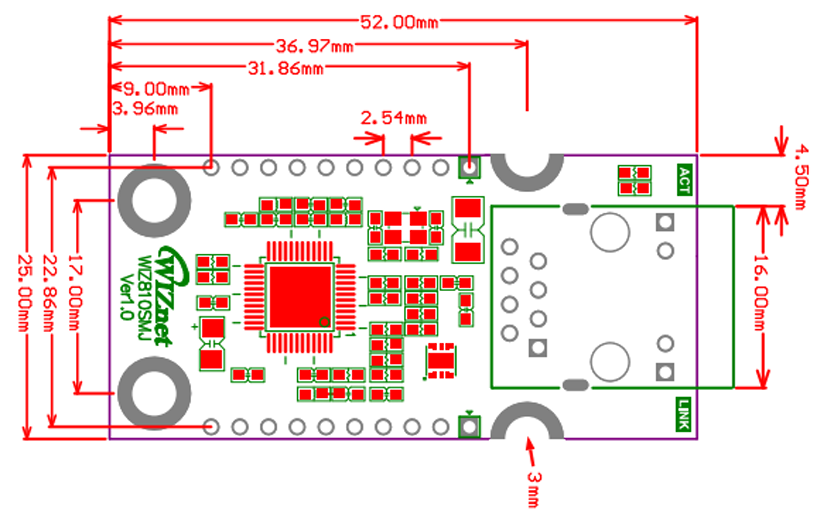

- Compact size: 2 × 10-pin headers (2.54 mm pitch)

- Operating temperature: −40 °C to +85 °C

Electrical Characteristics

- DC Characteristics

- Power Dissipation

| Symbol | Parameter | Pins | Min | Typ | Max | Unit |

|---|---|---|---|---|---|---|

| VDD | Supply voltage | 3.3 V | 2.97 | 3.3 | 3.63 | V |

| VIH | High-level input | ALL | 2.0 | – | - | V |

| VIL | Low-level input | ALL | – | – | 0.8 | V |

| VOH | High-level output | ALL | 2.4 | 3.3 | – | V |

| VOL | Low-level output | ALL | - | – | 0.4 | V |

| Condition | Min | Typ | Max | Unit |

|---|---|---|---|---|

| 100M Link | – | 93 | 110 | mA |

| 10M Link | – | 93 | 210 | mA |

| Un-Link (Auto-negotiation) | – | 43 | 170 | mA |

| Power Down mode | – | 10 | 20 | mA |

Documentation

| Title | Description | Link |

|---|---|---|

| User Manual | Technical documentation for WIZ810SMJ module |

Software Resources

- Driver

Driver

| Resource | Description |

|---|---|

| Official WIZnet driver library supporting W5100S and related Ethernet controllers |

Note: The ioLibrary_Driver is an MCU-independent software library that provides TCP/IP stack and application protocols (DHCP, DNS, HTTP, etc.) for WIZnet’s hardwired Ethernet chips.

Hardware Resources

| Title | Revision | Description | Download | Notes |

|---|---|---|---|---|

| schematic | 1.0 | Circuit diagram for hardware design reference | — | |

| 3D File | 1.0 | 3D model for mechanical design and visualization | — | |

| Part list | 1.0 | List of components used in the hardware | — |

Mechanical Information

- Form factor: ioModule with integrated RJ45 MAG-JACK

- Pin pitch: 2.54 mm (pin header)

- Dimensions: 52.00 x 25.00 (mm)

Related Products

| Product | Description |

|---|---|

| W5100S Chip | Hardwired TCP/IP Ethernet controller with PHY |

| WIZ810Sio | Compact SPI Ethernet module using W5100S |