WIZ610MJ

WIZ610MJ

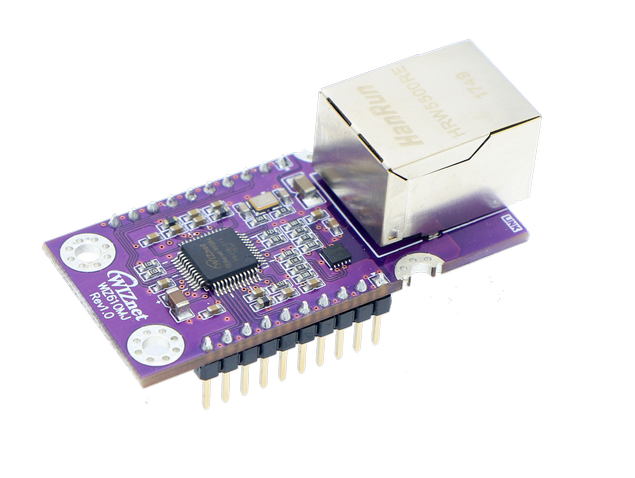

The WIZ610MJ is a compact Ethernet module that integrates the W6100 hardwired TCP/IP chip with an embedded PHY and an RJ45 MAG-JACK. It supports both IPv4 and IPv6 Dual Stack, enabling flexible networking for modern embedded systems. By combining all essential Ethernet hardware in one module, it eliminates complex PCB design for the transformer and RJ45 interface. The WIZ610MJ is ideal for developers who want to implement network-enabled systems quickly and reliably.

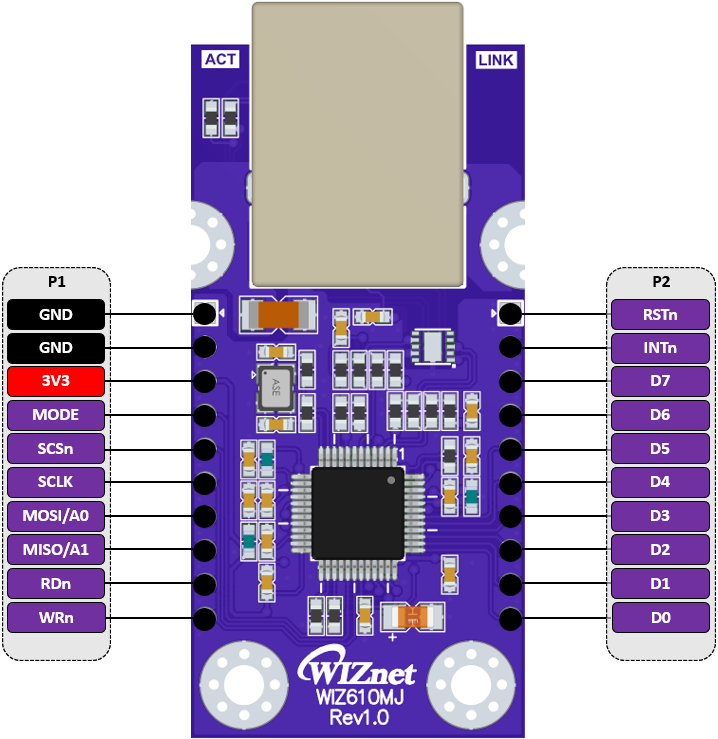

Pin Information

- All Pins

P1

| Pin | Type | Name | Description |

|---|---|---|---|

| 1 | P | GND | Ground |

| 2 | P | GND | Ground |

| 3 | P | 3V3D | 3.3 V Power |

| 4 | I | MODE | SPI/BUS Select pin SPI : Low BUS : High |

| 5 | I | SCSn | SPI Chip select (active low) |

| 6 | I | SCLK | SPI Clock input |

| 7 | I | MOSI/A0 | SPI : Master-Out / Slave-In BUS : A0 |

| 8 | O/I | MISO/A1 | SPI : Master-In / Slave-Out BUS : A1 |

| 9 | I | RDn | Read Strobe SPI : indicates Read Operation BUS : indicates Read Operation |

| 10 | I | WRn | Write Strobe SPI : indicates Read Operation BUS : indicates Write Operation |

P2

| Pin | Type | Name | Description |

|---|---|---|---|

| 1 | I | RSTn | Hardware reset (active low, ≥ 1 µs) |

| 2 | O | INTn | Interrupt output (low-active) |

| 3 | IO | D7 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 4 | IO | D6 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 5 | IO | D5 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 6 | IO | D4 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 7 | IO | D3 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 8 | IO | D2 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 9 | IO | D1 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 10 | IO | D0 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

Features

- Supports IPv4/IPv6 Dual Stack

- Hardwired Internet protocols: TCP, UDP, ICMPv6, ICMPv4, IGMP, MLDv1, ARP, PPPoE

- 8 independent sockets with 32 KB internal TX/RX buffer

- SOCKET-less commands for ARP, PING, and ICMPv6 (DAD, NA, RS)

- High-speed SPI interface (Mode 0/3)

- Parallel bus mode with 8-bit data and 2 address lines

- Auto-negotiation and Auto-MDIX (for 10/100 Mbps)

- Ethernet Power-down & Main Clock Switching for low-power operation

- Supports Wake-on-LAN (UDP)

- 2 × 10-pin headers (2.54 mm pitch)

- Operating temperature: −40 °C to +85 °C

Electrical Characteristics

- DC Characteristics

- Power Dissipation

| Symbol | Parameter | Pins | Min | Typ | Max | Unit |

|---|---|---|---|---|---|---|

| VDD | Supply voltage | 3.3 V | 2.97 | 3.3 | 3.63 | V |

| VIH | High-level input | ALL | 2.0 | – | - | V |

| VIL | Low-level input | ALL | – | – | 0.8 | V |

| VOH | High-level output | ALL | 2.4 | 3.3 | – | V |

| VOL | Low-level output | ALL | 0.0 | – | 0.4 | V |

| IDD | Supply current (Normal) | 3.3 V | – | 132 | – | mA |

| IPD | Supply current (Power-down) | 3.3 V | – | 13 | – | mA |

| Condition | Min | Typ | Max | Unit |

|---|---|---|---|---|

| 100M Link | – | 98 | 115 | mA |

| 10M Link | – | 112 | 265 | mA |

| 10M-Te Link | – | 75 | 190 | mA |

| 100M Unlink | – | 50 | 199 | mA |

| 10M Unlink | – | 26 | 170 | mA |

| 10M-Te Unlink | – | 26 | 130 | mA |

| Un-Link (Auto-negotiation mode) | – | 50 | 199 | mA |

| Power Down mode | – | 14 | 20 | mA |

Documentation

| Title | Description | Link |

|---|---|---|

| Datasheet | Technical datasheet for WIZ610MJ module |

Software Resources

- Driver

Driver

| Resource | Description |

|---|---|

| Official WIZnet driver library supporting W6100 and other Ethernet controllers |

Note: The ioLibrary_Driver provides MCU-independent implementations of TCP/IP services for WIZnet chips.

Includes DHCP, DNS, SNTP, MQTT, TFTP, and HTTP server modules.

Hardware Resources

| Title | Revision | Description | Download | Notes |

|---|---|---|---|---|

| schematic | 1.0 | Circuit diagram for hardware design reference | — | |

| 3D File | 1.0 | 3D model for mechanical design and visualization | — | |

| Part list | 1.0 | List of components used in the hardware | — |

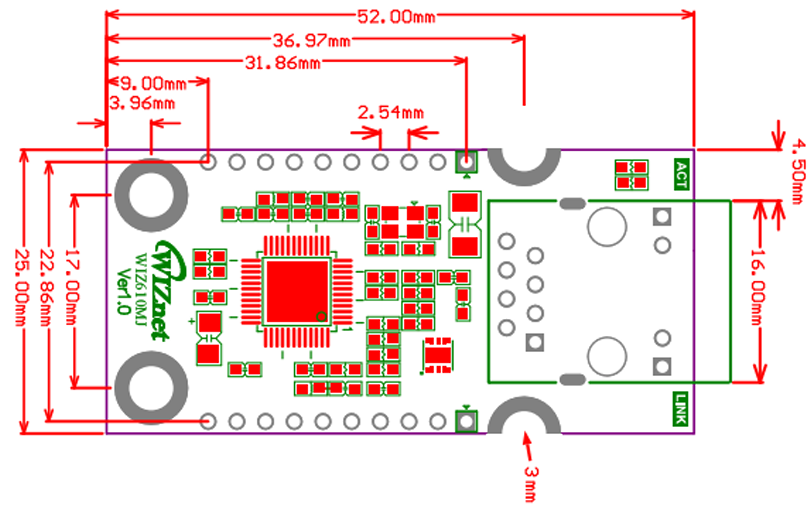

Mechanical Information

- Form factor: Compact ioModule with integrated RJ45 MAG-JACK

- Pin pitch: 2.54 mm (2 × 10 header)

- Dimensions: 28.0 × 28.0 mm (typ.)

Related Products

| Product | Description |

|---|---|

| W6100 Chip | Stand-alone W6100 Ethernet controller (IPv4/IPv6 Dual Stack) |

| WIZ610io | Compact SPI Ethernet module using W6100 chip |

| W5500-io | Compact SPI Ethernet module using W5500 chip |