WIZ-IP51s

WIZ-IP51s

The WIZ-IP51s is a network offloading module that integrates the W5100S chip (with built-in PHY physical layer and TCP/IP hardware protocol stack) and an RJ45 connector with integrated network transformer. As a plug-and-play component, it enables seamless interface connection between the W5100S and the transformer without the need for additional circuit design.

For users who wish to quickly develop networked systems, the WIZ-IP51S is an ideal choice.

All technical issue for WIZIP-51S , please contact WIZnet HK.

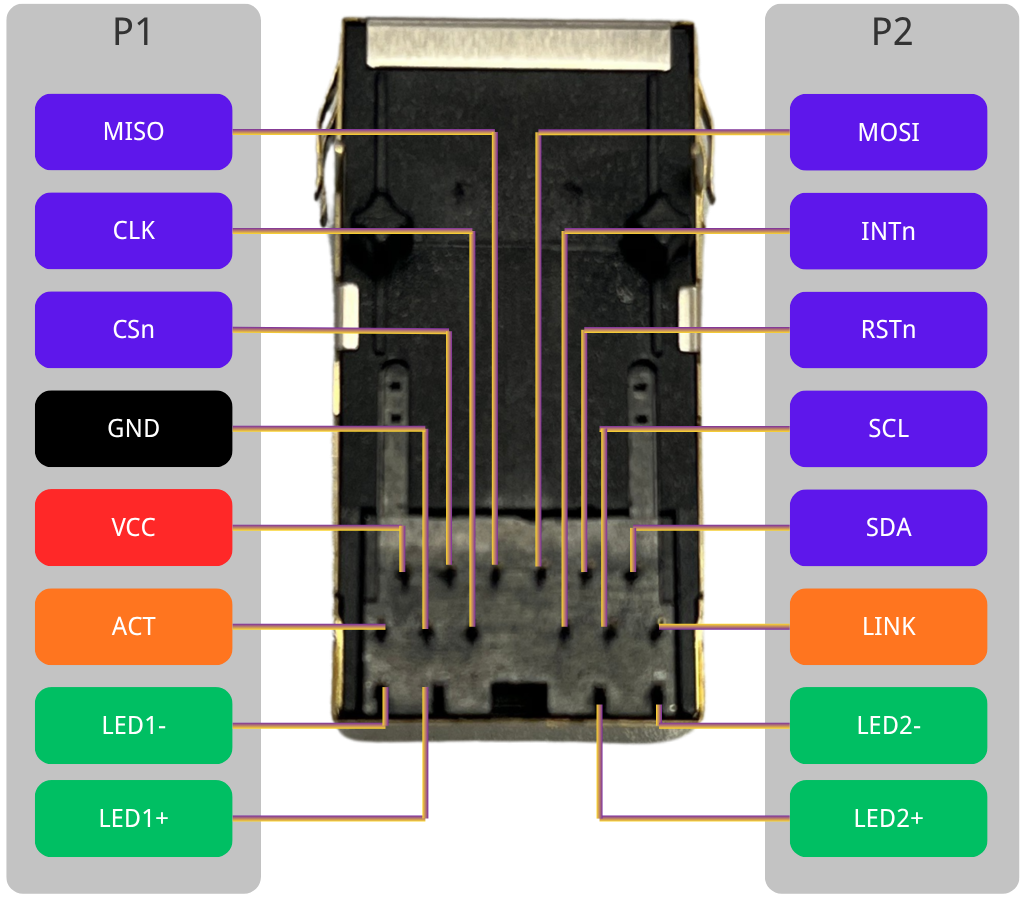

Pin Information

- All

P1

| Pin | Type | Name | Description |

|---|---|---|---|

| 1 | I | MISO | SPI Master-In / Slave-Out |

| 2 | I | CLK | SPI clock input |

| 3 | I | CSn | SPI Master-Out / Slave-In |

| 4 | P | GND | Ground |

| 5 | P | VCC | 3.3 V Power supply |

| 6 | O | ACT | Activity LED signal |

| 7 | – | LED1- | Connect to ACT |

| 8 | – | LED1+ | Connect in series with resistor to VCC |

P2

| Pin | Type | Name | Description |

|---|---|---|---|

| 1 | I | MOSI | SPI Master-Out / Slave-In |

| 2 | I | INTn | Interrupt output (low-active) — indicates socket events like connection, disconnection, data reception, and WOL |

| 3 | I | RSTn | Hardware reset input (active low, ≥ 500 µs) |

| 4 | I | SCL | IIC clock line |

| 5 | I | SDA | IIC data cable |

| 6 | O | LINK | Network connection LED signal |

| 7 | – | LED2- | Connect to LINK |

| 8 | – | LED2+ | Connect in series with resistor to VCC |

Wait at least 50 ms after RSTn goes high before SPI communication.

Features

- Supports full hardware TCP/IP protocol: TCP, UDP, WOL, ICMP, IGMPv1/v2, IPv4, ARP, PPPoE

- Supports SOCKET-less instructions: ARP-request, PING-request

- Supports 4 independent SOCKET concurrent communication

- Supports half-duplex/full-duplex operation mode

- Supports Ethernet power-off mode and master clock selection energy-saving mode

- Supports UDP-based network wake-up (WOL) function

- High-speed SPI interface (MODE 0/3)

- Built-in total 16Kbytes of send/receive cache

- Integrated 10BaseT/100BaseTX Ethernet PHY

- Supports Ethernet auto-negotiation (full/half-duplex, 10Base-T/100Base-TX)

- Supports Auto-MDIX function (only supported in Ethernet auto-negotiation mode)

- Operating voltage: 3.3V (I/O compatible with 5V signal voltage)

- 19-pin pin header interface

- Package size (length×width×height):32.5×16.5×17.3(mm)

- Compatible with WIZnet's IO module carrier board development board

Electrical Characteristics

- DC Characteristics

- Power Dissipation

| Symbol | Parameter | Pins | Min | Typ | Max | Unit |

|---|---|---|---|---|---|---|

| VDD | Supply voltage | 3.3 V | 2.97 | 3.3 | 3.63 | V |

| VIH | High-level input | ALL | 2.3 | – | 5.5 | V |

| VIL | Low-level input | ALL | –0.3 | – | 0.9 | V |

| VOH | High-level output | ALL | 2.9 | 3.3 | – | V |

| VOL | Low-level output | ALL | 0.0 | – | 0.52 | V |

| IDD | Supply current (Normal) | 3.3 V | 124 | 130 | 137 | mA |

| Condition | Min | Typ | Max | Unit |

|---|---|---|---|---|

| 100 Mb/s Link | – | 93 | 110 | mA |

| 10 Mb/s Link | – | 93 | 210 | mA |

| Unlink (Auto-negotiation) | – | 43 | – | mA |

| 100 Mb/s Tx | – | 40 | 170 | mA |

| 10 Mb/s Tx | – | 25 | 150 | mA |

Documentation

This section provides key documentation, including user manuals and datasheets, to help you understand product features, specifications, and usage.

| Title | Description | Link | Notes |

|---|---|---|---|

| Datasheet | Technical specifications and features of the W5100s chip | - |

SPI operation of WIZ-IP51s follows W5100S. For more information about SPI operation of W5100s, please refer to W5100s Datasheet.

Software Resources

- Driver

- Application Note

Driver

| Resource | Description |

|---|---|

| Official WIZnet driver library for W5100s and other chips |

The ioLibrary_Driver is an MCU-independent library for WIZnet W5x00, W6x00 chips .

It provides implementations of essential TCP/IP services, enabling developers to build network applications with minimal MCU dependencies.

Supported services

DHCP, DNS, MQTT, SNTP, TFTP, HTTP Server

Application Note

| Name | Description | Notes |

|---|---|---|

| How to use IPRAW Mode | IPRAW Mode handles IPv4 layer communication | |

| How to use IPRAW Mode | IPRAW Mode handles IPv4 layer communication | |

| How to use IPRAW Mode | IPRAW Mode handles IPv4 layer communication | |

| How to use PPP/PPPoE | PPP is Link-Layer protocol for point-to-point | |

| Non-Socket ARP and PING process | Command based handling ARP and PING processing | |

| Interrupt example | Publishes messages to broker | |

| How to use IPRAW Mode | IPRAW Mode handles IPv4 layer communication |

These application notes explain how to use W5500's core networking functions including TCP, UDP, IPRAW mode, and PPPoE protocols.

Hardware Resources

| Title | Revision | Description | Download | Notes |

|---|---|---|---|---|

| Schematic | 1.0 | Circuit diagram for reference | TBD |

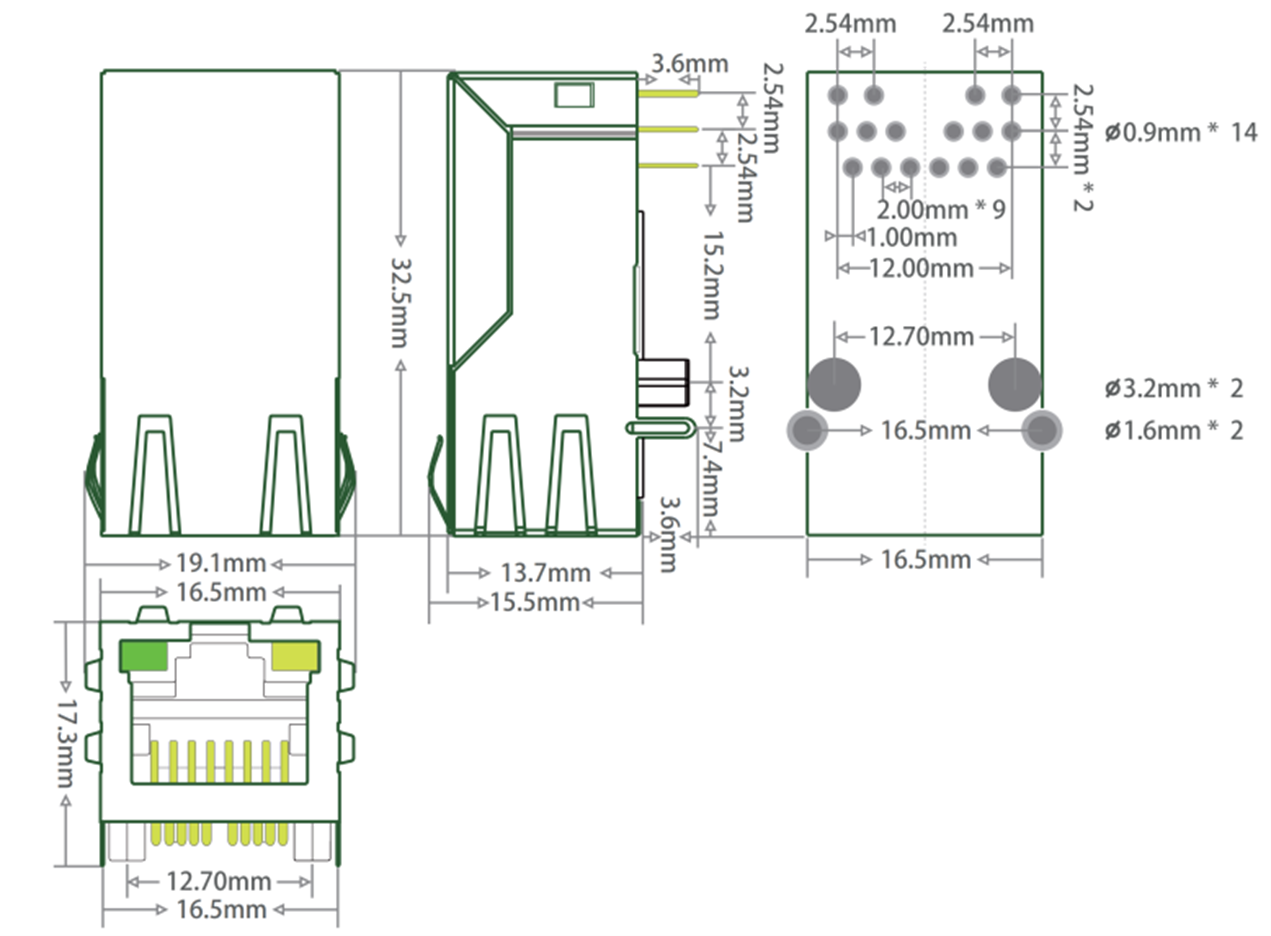

Mechanical Information

- Form factor: Plug-in Port module

- Pin pitch: 2.54 mm

- Dimensions: 32.5 × 16.5 mm

Related Products

| Product | Description |

|---|---|

| W5100S Chip | Hardwired TCP/IP Ethernet controller with integrated PHY |