WIZ750SR-105 Datasheet

Hardware Specification

Product Spec Table

| Category | Description | |

|---|---|---|

| MCU | ARM Cortex-M0 Core | W7500 48Mhz maximum frequency Internal 8Mhz RC Oscillator Flash: 128KB Large flexible-size SRAM buffer for various User Application - Min 16KB available if full 32KB socket buffer used - Max 48KB available if no socket buffer used ROM for boot code: 6 KB |

| MCU | Hardwired TCP/IP Core | 8 independent Sockets SRAM for socket: 32KB MII (Medium-Independent Interface) TCP/IP Protocols: TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE |

| PHY | Transceiver | IP101GRI Single 10/100M Ethernet Transceiver |

| Serial | Interface | WIZ750SR-105: TTL Version WIZ105SR-EVB: RS-232 Version |

| Serial | Signal | TXD, RXD, RTS, CTS, GND |

| Serial | Parameters | Parity: None, Odd, Even Data bits: 7, 8 bit Flow control: None, RTS / CTS, XON / XOFF |

| Serial | Speed | Up to 230Kbps |

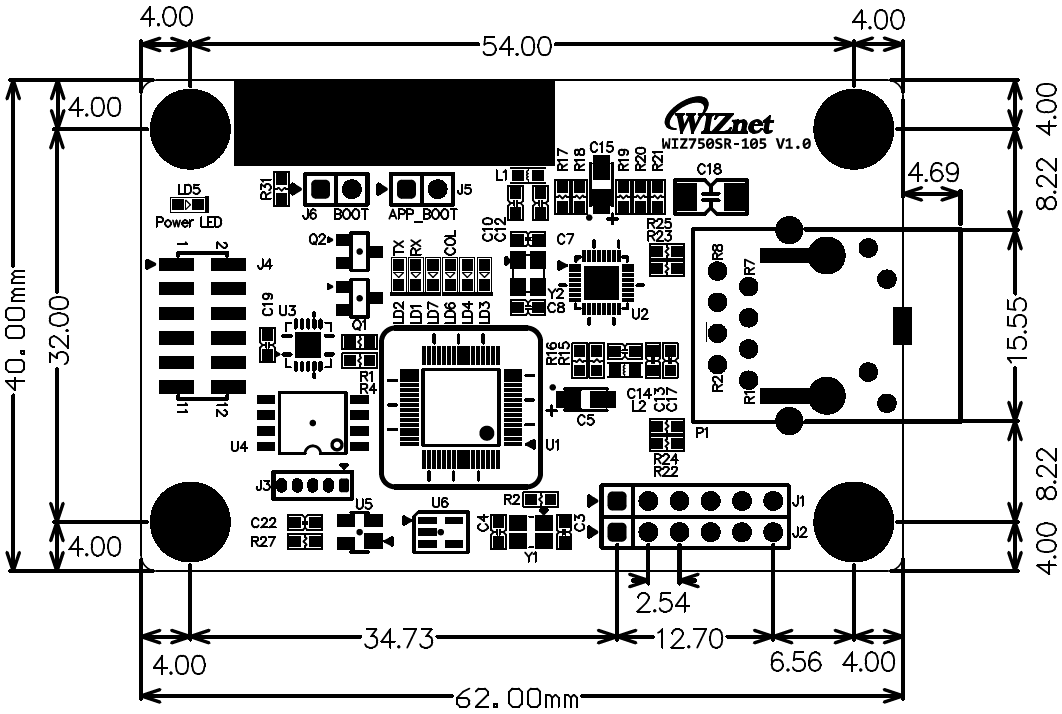

| Dimension | 62mm x 40mm (PCB board size) 62mm x 40mm x 18mm (Include part size) | |

| Connector type | RJ-45(Ethernet Connector) 2.00mm Pitch 2x6 SMD Pin-header(Data Line) | |

| Input Voltage | DC 3.3V, 100mA under | |

| Temperature | -40℃ ~ 85℃ (Operation), -40℃ ~ 85℃ (Storage range) |

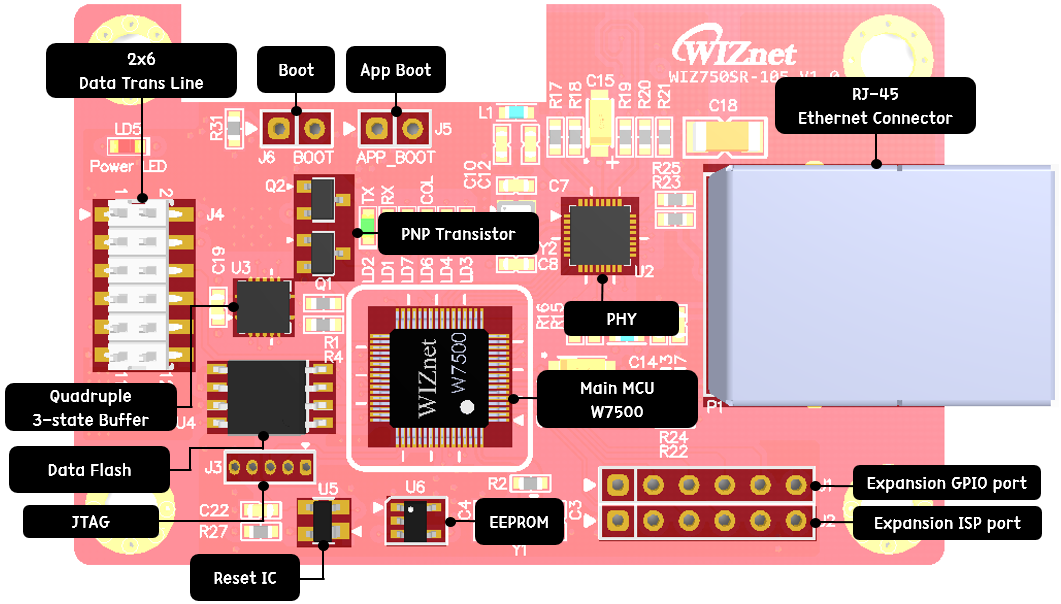

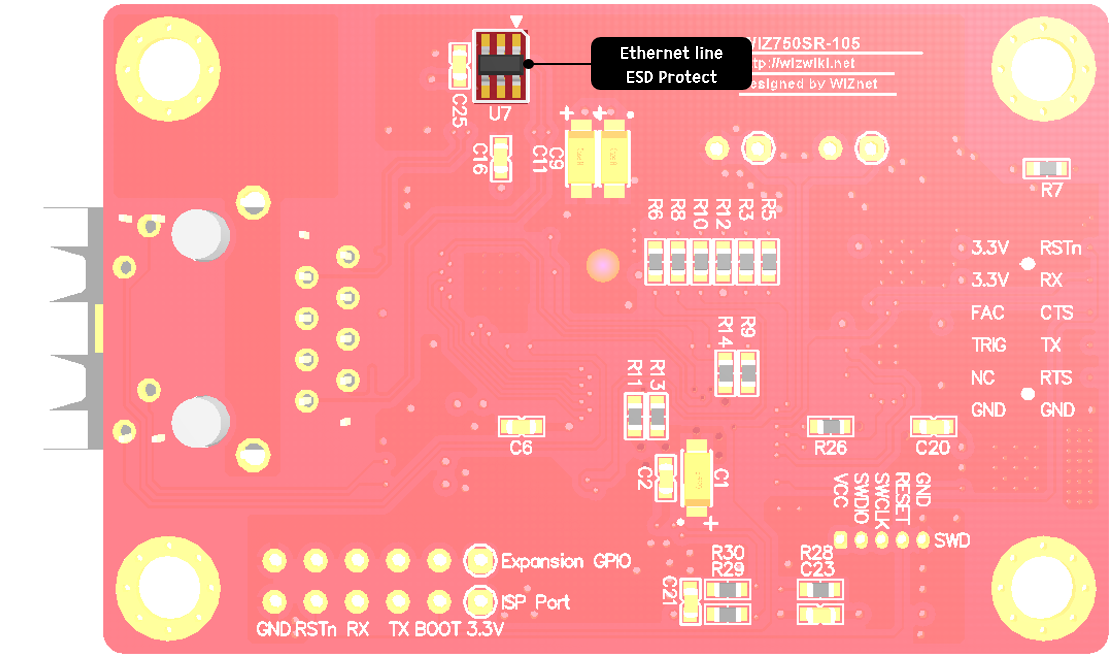

WIZ750SR-105 Callout

|

| TOP |

|

| BOTTOM |

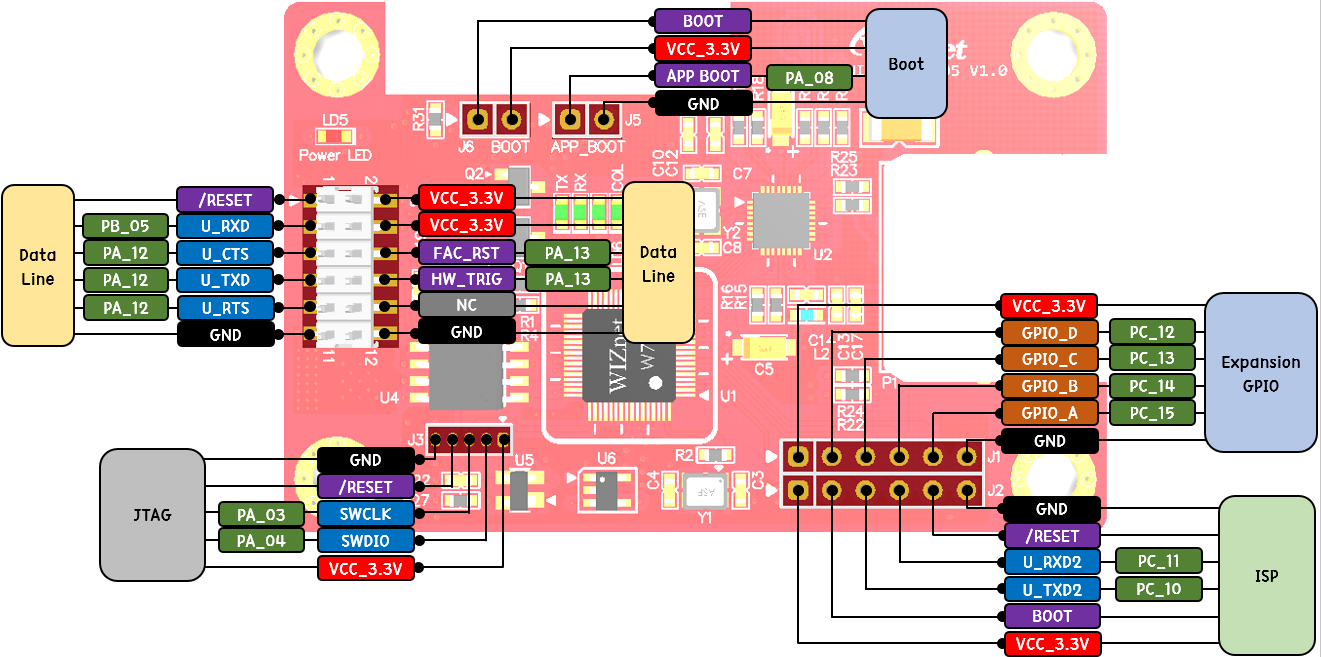

WIZ750SR-105 Pinout

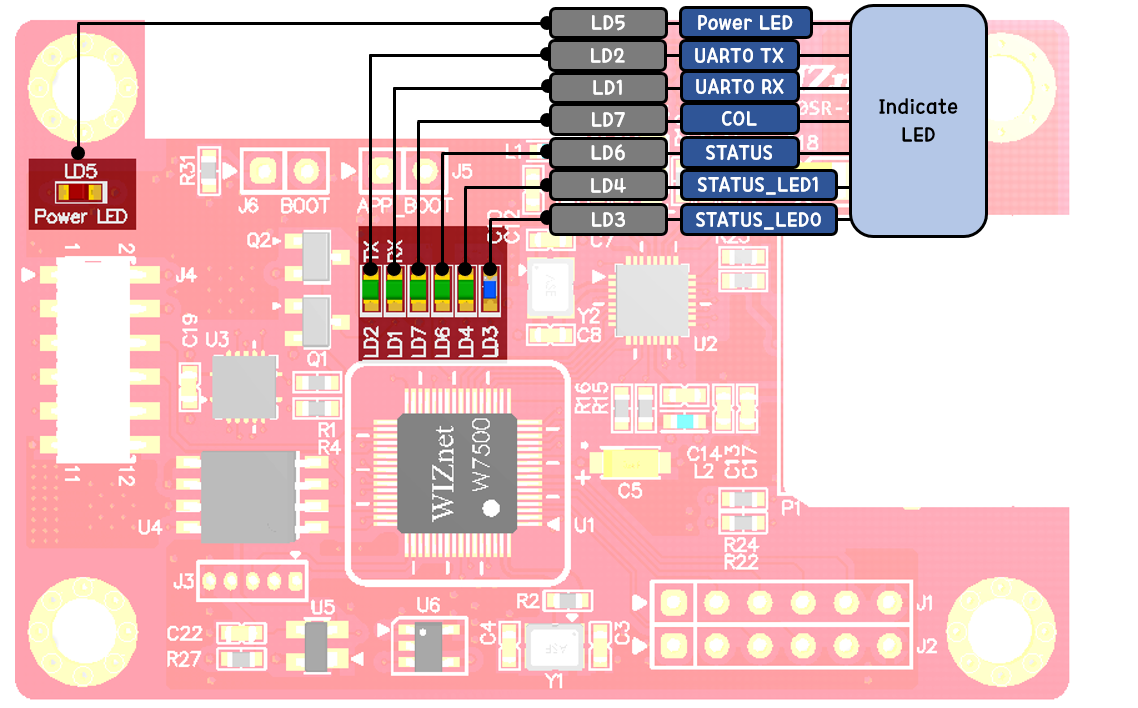

WIZ750SR-105 indicate

| Pin Number | Pin Name | Signal | Description |

|---|---|---|---|

| 1 | LD1 | UART0 RX | UART receiver indicate |

| 2 | LD2 | UART0 TX | UART Transceiver indicate |

| 3 | LD3 | Status_LED0 | PHY LINK check or initialize done |

| 4 | LD4 | Status_LED1 | TCP Connection |

| 5 | LD5 | Power LED | - |

| 6 | LD6 | STATUS | Not function |

| 7 | LD7 | COL | Collision Detected |

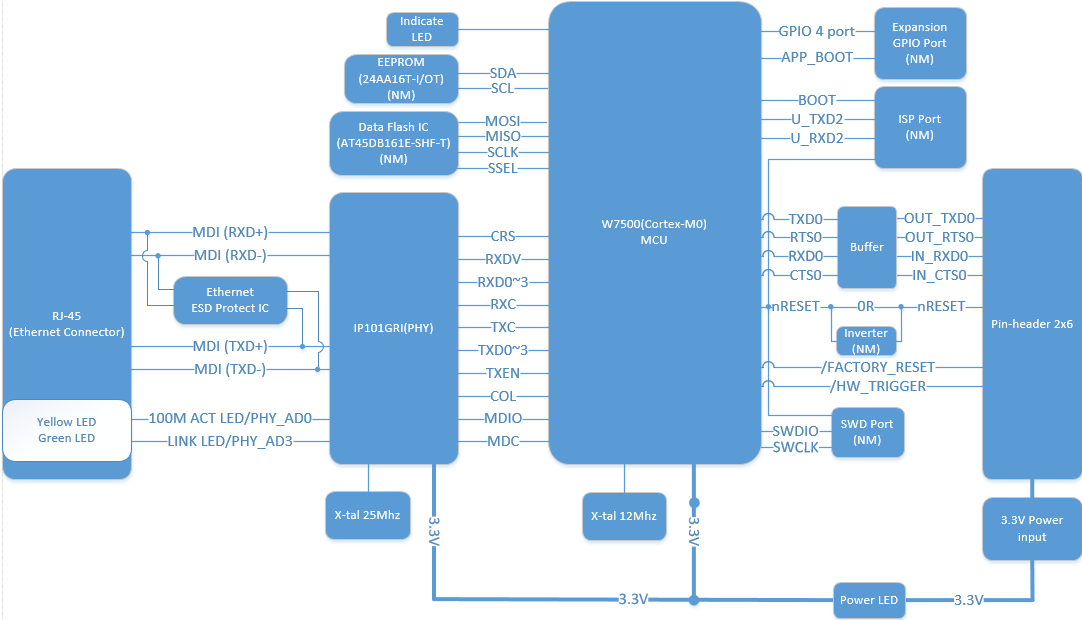

WIZ750SR-105 Block Diagram

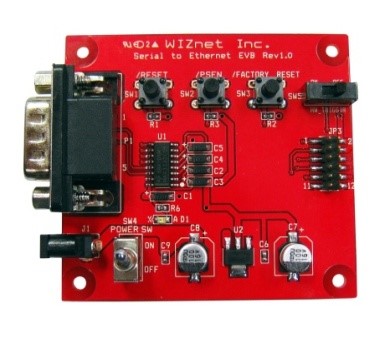

WIZ105SR-EVB

- WIZ750SR-105 Developer Interface Board.

- RESET Tact SW.

- FACTORY RESET SW.

- BOOT0 Slide SW.

- H/W Trig Slide SW.

- RS-232C Transceiver, D-SUB9-MALE.

- 5V DC-JACK (External 4.5pi, internal 1.3pi)

- inside LDO 3.3V (5V to 3.3V)

WIZ750SR-105 EVB is must use the WIZ105SR-EVB Because WIZ750S-105 is a replacement for WIZ105SR.

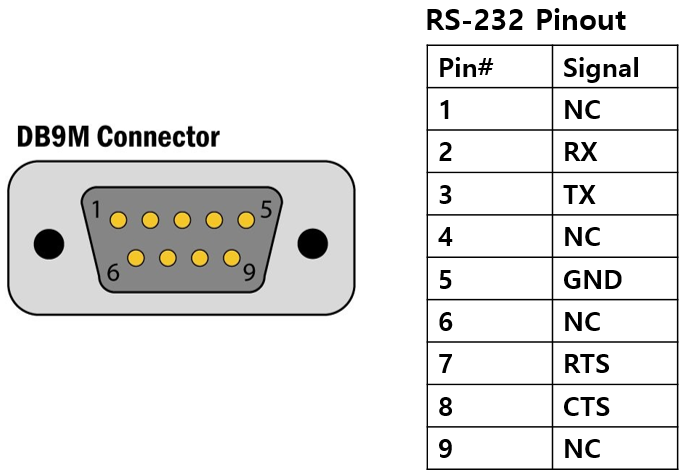

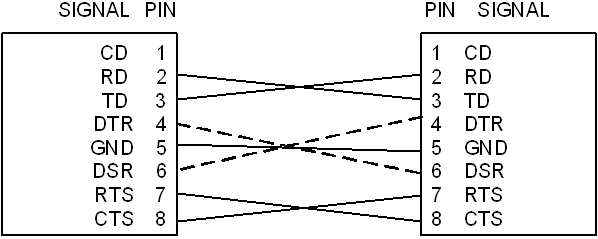

Serial Interface

| Pin Number | Signal | Description |

|---|---|---|

| 1 | DCD | NC |

| 2 | RXD | Receive Data |

| 3 | TXD | Transmit Data |

| 4 | DTR | NC |

| 5 | GND | System Ground(Signal Ground) |

| 6 | DSR | NC |

| 7 | RTS | Request To Send |

| 8 | CTS | Clear To Send |

| 9 | RI | NC |

- RXD, TXD, GND: These are all you need if the device does not use hardware handshaking.

- RXD, TXD, GND, RTS, CTS: These are the signals used when serial device uses hardware handshaking.

- DTR, DSR: Not used

Schematic & Artwork

WIZ750SR-105

| H/W version | Type | Filetype | Download Link | Remarks |

|---|---|---|---|---|

| 1.0 | TTL | Altium | - | |

| ::: | ::: | - |

3D File

| H/W version | Type | Filetype | Download Link | Remarks |

|---|---|---|---|---|

| 1.0 | TTL | Altium | - |

Part list

WIZ750SR-105

| H/W version | Type | Filetype | Download Link | Remarks |

|---|---|---|---|---|

| 1.0 | TTL | Excel | - | |

| ::: | ::: | - |

Electrical Characteristics

Operating Conditions

| Symbol | Parameter | Pins | Min | Typ | Max | Unit |

|---|---|---|---|---|---|---|

| Vcc | Operating Voltage | 3.3V | 3.135 | 3.3 | 3.465 | V |

| Vss | Ground | ALL | 0 | 50 | mV | |

| fFCLK | Internal CPU clock frequency | ALL | 0 | - | 48 | MHz |

| Tstg | Storage Temperature (max) | ALL | -40 | 85 | ℃ | |

| TA | Ambient operating temperature | ALL | -40 | 85 | ℃ | |

| VIO | I/O Signal voltage (Tolerance) | ALL | Vss-0.3 | 3.3 | 5 | V |

| VIH | Input high voltage | ALL | 2.5 | V | ||

| VIL | Input low voltage | ALL | 0.6 | V | ||

| VOH | Output high voltage (High driving strength Current load = 6mA) (Low driving strength Current load = 3mA) | ALL | 2.83 | V | ||

| VOL | Output high voltage (High driving strength Current load = 6mA) (Low driving strength Current load = 3mA) | ALL | 0.32 | V |

Flash Memory

| Symbol | Parameter | Min | Unit |

|---|---|---|---|

| NEND | Sector Endurance | 10,000 | Cycles |

| TDR | Data Retention | 10 | Years |

EEPROM

| Symbol | Parameter | Min | Unit |

|---|---|---|---|

| NEND | Sector Endurance | 1M | Cycles |

| TDR | Data Retention | 200 | Years |

Connector Specification

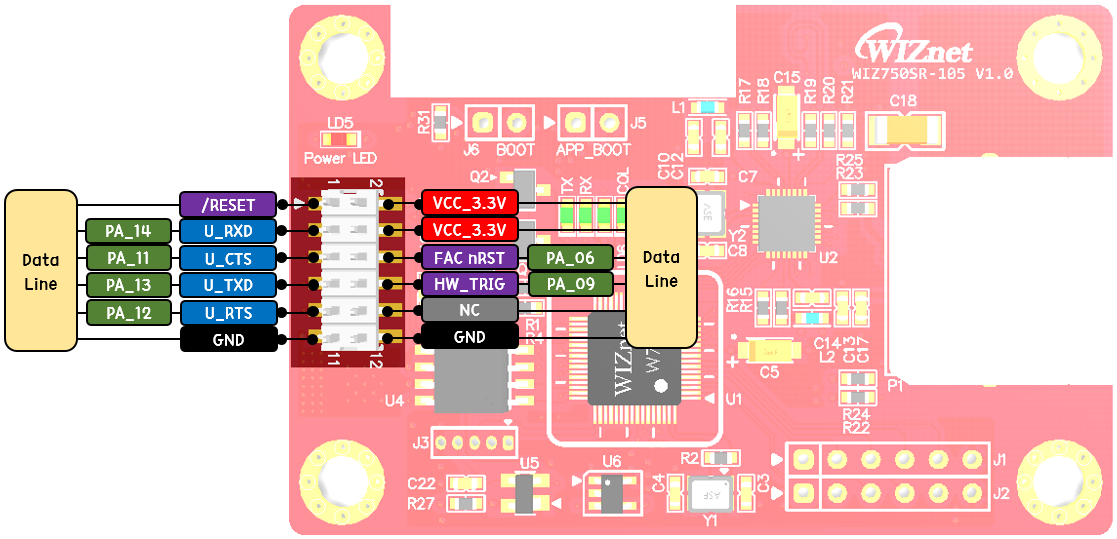

6x2 Data Pin Connector (J4)

| Pin Number | Signal | Description |

|---|---|---|

| 1 | nRESET | System Reset signal (Active Low) |

| 2 | VCC | System Power (3.3V) |

| 3 | U_RXD0 | Receive Data (TTL : 3.3V) |

| 4 | VCC | System Power (3.3V) |

| 5 | U_CTS0 | Clear To Send (TTL : 3.3V) |

| 6 | FAC_nRST | System Reset signal (Active Low) |

| 7 | U_TXD0 | Transmit Data (TTL : 3.3V) |

| 8 | HW_TRIG | Hardware Trigger signal (Active Low) |

| 9 | U_RTS0 | Request To Send (TTL : 3.3V) |

| 10 | NC | Not Connect |

| 11 | GND | System Ground |

| 12 | GND | System Ground |

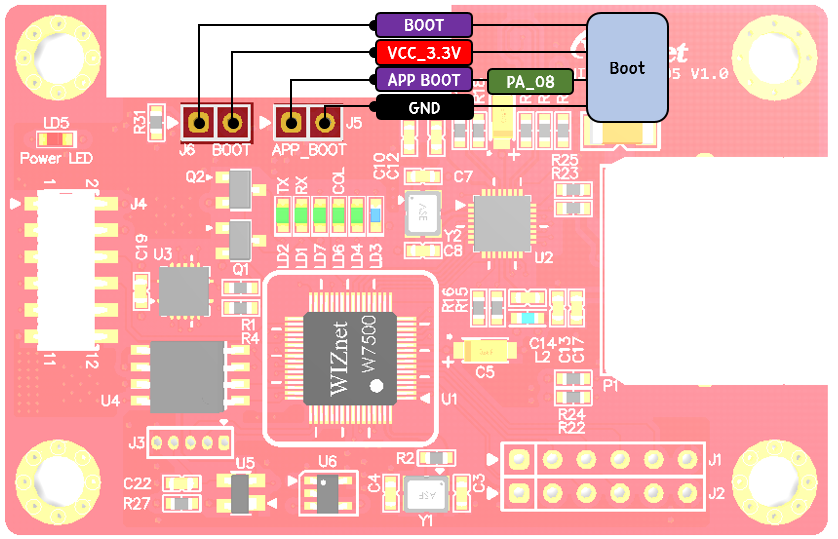

BOOT Pin (J5, J6)

| Parts | Pin Number | Signal | Description |

|---|---|---|---|

| J5 | 1 | APP BOOT | Application Jump at BOOT mode |

| ::: | 2 | GND | System Ground |

| Parts | Pin Number | Signal | Description |

|---|---|---|---|

| J6 | 1 | BOOT | System Ground |

| ::: | 2 | VCC | System Power (3.3V) |

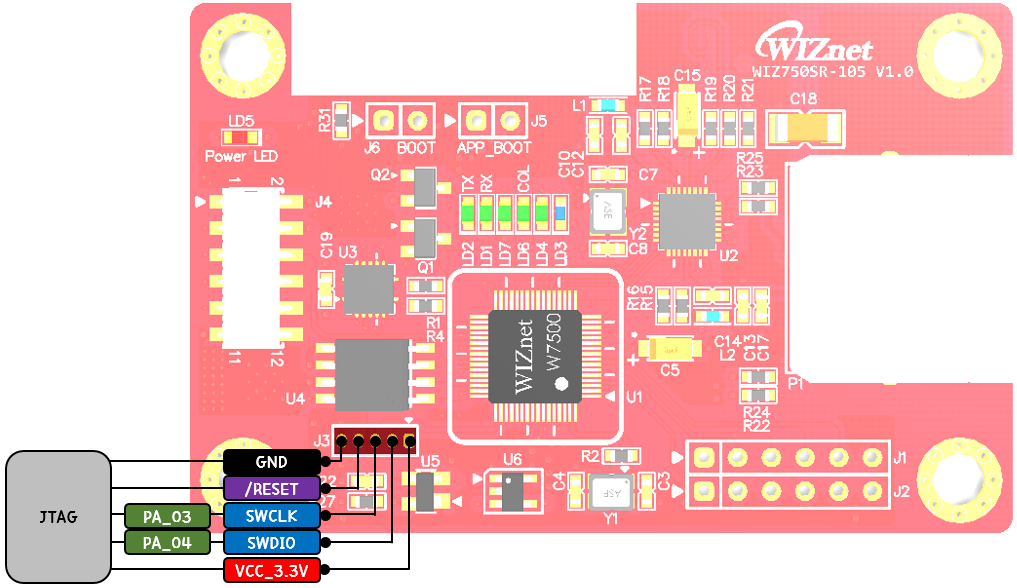

SWD(JTAG) Pin (J3)

| Pin Number | Signal | Description |

|---|---|---|

| 1 | VCC | System Power (3.3V) |

| 2 | SWDIO | SWD(JTAG) Data I/O pin |

| 3 | SWCLK | SWD(JTAG) Clock pin |

| 4 | nRESET | System Reset signal (Active Low) |

| 5 | GND | System Ground |

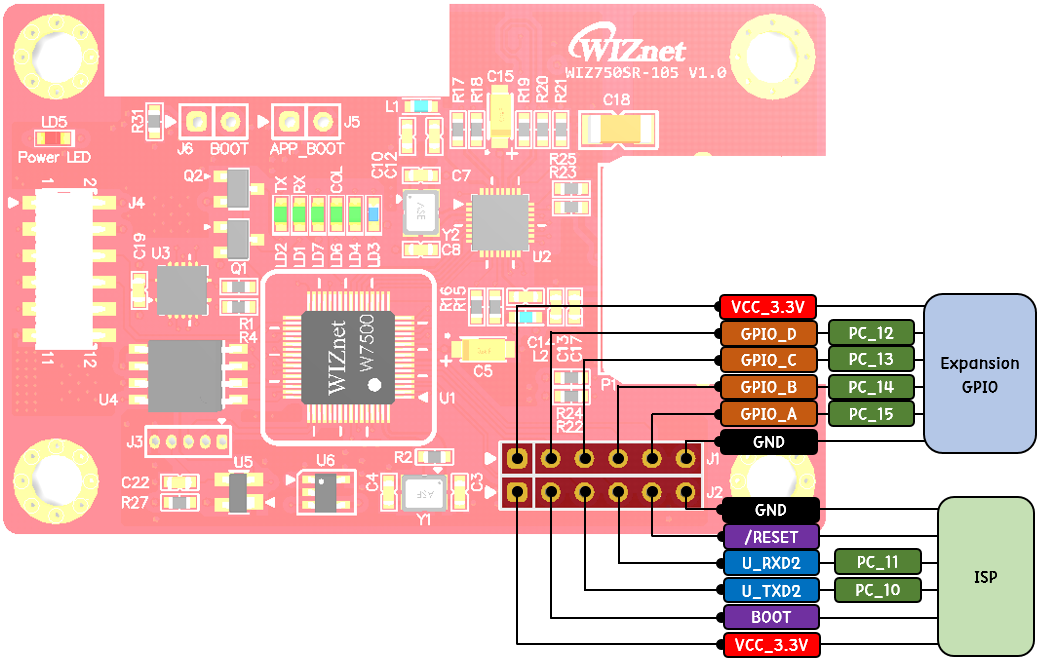

ISP Port & Expansion GPIO (J1, J2)

| Parts | Pin Number | Signal | Description |

|---|---|---|---|

| J1 | 1 | VCC | System Power (3.3V) |

| ::: | 2 | Expansion GPIOD | Expansion User's depend on GPIO port |

| ::: | 3 | Expansion GPIOC | ::: |

| ::: | 4 | Expansion GPIOB | ::: |

| ::: | 5 | Expansion GPIOA | ::: |

| ::: | 6 | GND | System Ground |

| Parts | Pin Number | Signal | Description |

|---|---|---|---|

| J2 | 1 | VCC | System Power (3.3V) |

| ::: | 2 | BOOT | BOOT SW |

| ::: | 3 | U_TXD2 | Simple UART2(Debug port) ISP mode firmware downloader port |

| ::: | 4 | U_RXD2 | Simple UART2(Debug port) ISP mode firmware downloader port |

| ::: | 5 | nRESET | System Reset signal (Active Low) |

| ::: | 6 | GND | System Ground |

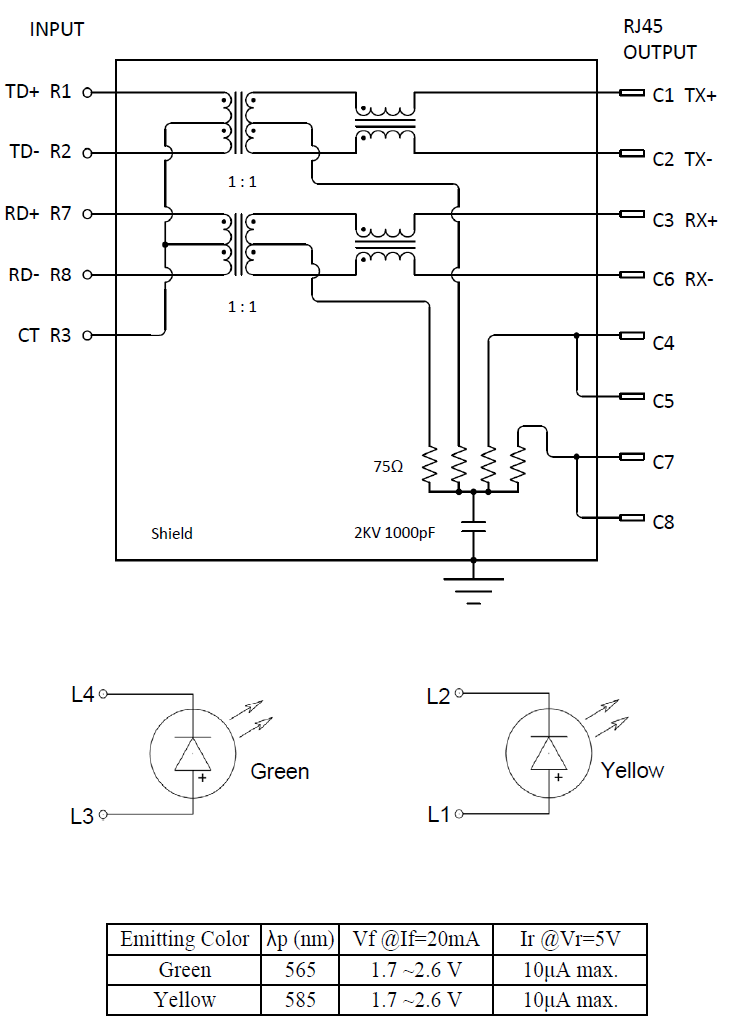

RJ-45 Connector (BS-RB10005)

| Pin Number | Pin | Signal |

|---|---|---|

| 1 | R1 | TX+ |

| 2 | R2 | TX- |

| 3 | R3 | TCT/RCT(Center tap) |

| 4 | R7 | RX+ |

| 5 | R8 | RX- |

| 6 | L1+(Active LED) | Anode |

| 7 | L2- (Active LED) | Cathode |

| 8 | L3+(LINK LED) | Anode |

| 9 | L4- (LINK LED) | Cathode |

Dimension

- WIZ750SR-105 Rev1.0 Dimension :

- 62mm x 40mm ( PCB board size )

- 62mm x 40mm x 18mm ( Included part size )