W5300

Chip Overview

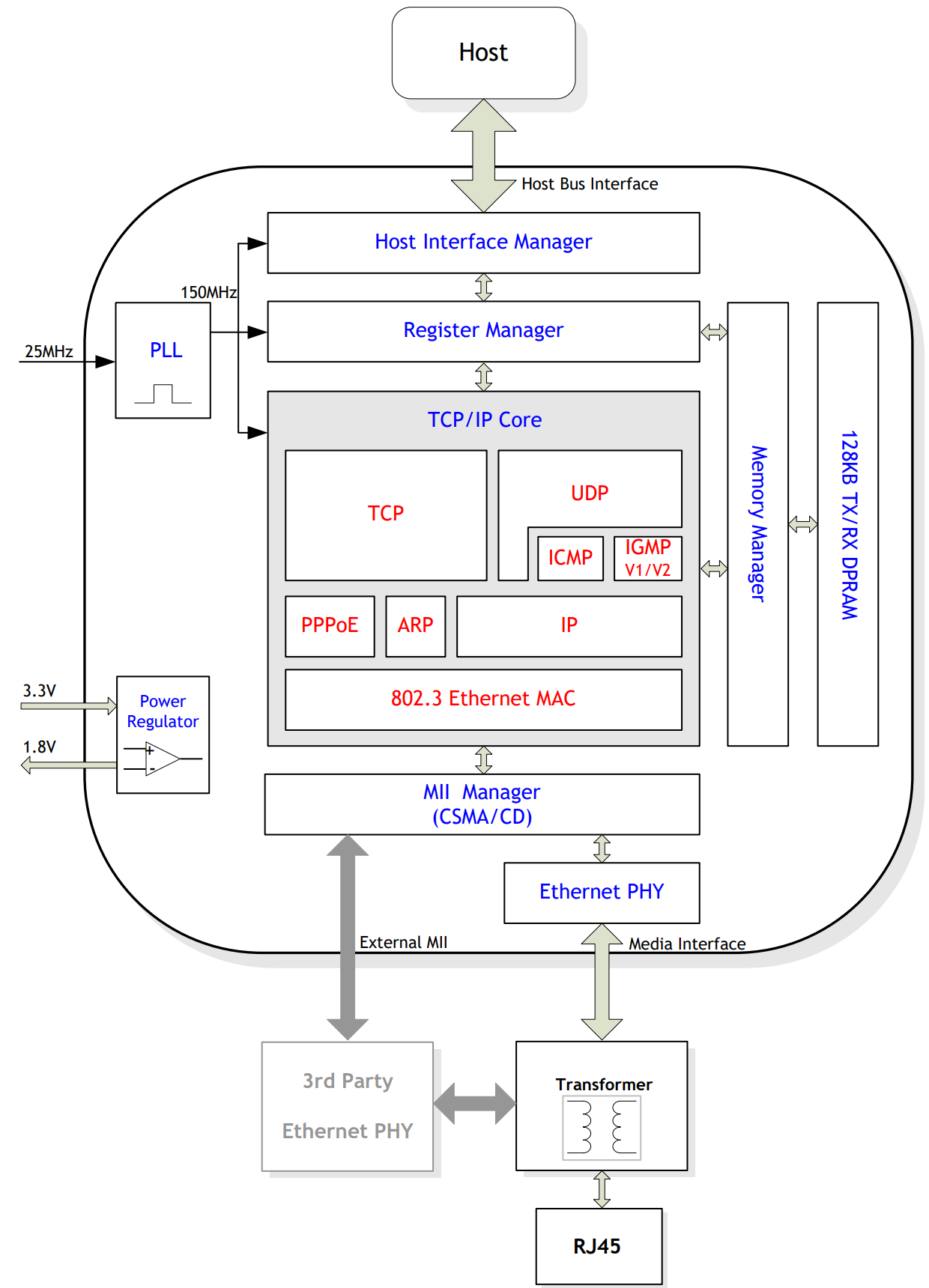

Hardwired Dual TCP/IP Stack Controller

The W5300 chip is a Hardwired TCP/IP embedded Ethernet controller that enables easier internet connection for embedded systems that require high network performance.

W5300 suits users in need of stable internet connectivity best, using a single chip to implement TCP/IP Stack, 10/100 Ethernet MAC and PHY. Hardwired TCP/IP stack supports TCP, UDP, IPv4, ICMP, ARP, IGMP, and PPPoE, …, which has been proven through various applications over many years. W5300 uses a 128Kbytes internal buffer as its data communication memory.

By using W5300, users can implement the Ethernet application they need by using a simple socket program instead of handling a complex Ethernet Controller. It is possible to use 8 independent hardware sockets simultaneously. BUS (Direct & Indirect) is provided for easy integration with the external MCU. The W5300 supports max. 80Mbps network throughput.

Features

- Hardwired TCP/IP protocols : TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE

- Un-attackable hardware network engine for preventing network attacks such as flooding, spoofing, injection

- Host Interface : 8/16 bit Data Bus (Direct & Indirect Address Mode)

- High Network Performance : Max 80Mbps (by DMA)

- Support embedded OS driver : Linux (kernel 2.6.24)

- 8 Independent hardware socket

- Internal 128Kbytes memory for TCP/IP packet processing

- Flexible memory allocation

- 10BaseT / 100Base TX Ethernet PHY Embedded

- Support Auto-Negotiation (Full & Half Duplex, 10 & 100 Based)

- Support Auto-MDIX

- 3.3V Operation with 5V I/O signal tolerance

- LED outputs (TX, RX, full/half duplex, Collision link speed)

- 100LQFP lead-free package (14x14mm)

Documents

- Datasheet

- Download Datasheet : Kr, Eng

Schematic

Related EVB

- Description of W5300-EVB

- Features

- Hardware Specification

- Download