# W55MH32 Datasheet

Version 1.0.0

© Copyright 2024 WIZnet Co., Ltd. All rights reserved.

# W55MH32

Enhanced, True Random Number, Hardware Encryption Algorithm Unit, 32-bit MCU with 1024KB Flash, 10/100 Ethernet MAC and PHY, Hardware Internet controller with an integrated full TCP/IP stack, USB, CAN, 17 Timers, 3 ADCs, 2 DACs, Up to 12 communication interface

# Features:

- Encapsulation

- W55MH32L:100QFN

- W55MH32Q:68QFN

- Core: 32-bit Arm® Cortex®-M3 Core

Up to 216MHz operation

frequency 2 54DMins (MHz(CoreMark) 10

- frequency, 2.54DMips/MHz(CoreMark1.0)

Single-cycle multiplication and hardware division

- Memories

- 1024K bytes of Flash memory

- 96Kbytes of SRAM

- Clock, reset and supply management

- 2.0~3.6V application supply and I/Os

- POR, PDR, and programmable voltage detector (PVD)

- 4 ~ 16MHz crystal oscillator

- Internal 8MHz factory-trimmed RC

- Internal 40kHz RC oscillator with calibration

- 32kHz RTC oscillator with calibration

- Low-power

- Sleep, Stop and Standby modes

- supply for RTC and backup registers

- 3 x 12-bit, 1 µs A/D converters (up to 12 channels)

- Conversion range: 0 to 3.6V

- Temperature sensor

- 2 x 12-bit D/A converters

- DMA: 12-channel DMA controller

- Ethernet: 10/100M Ethernet MAC and PHY

- Supports following Hardwired TCP/IP Protocols : TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE

- Supports 8 independent sockets simultaneously

- Internal 32Kbytes Memory for Tx/Rx Buffers

- 10BaseT/100BaseTX Ethernet PHY embedded

- Support Auto Negotiation (Full and half duplex, 10 and 100-based)

- LED outputs (Full/Half duplex, Link,Speed, Active)

- Debug mode

- Serial wire debug (SWD) & JTAG interfaces

Embedded Tracking Module(ETM)

- I/O ports

- 66(W55MH32L) / 36(W55MH32Q) multifunction bidirectional I/O ports, all mappable on 16 external interrupts

- All GPIOs can be forced to configure pull-up and pull-down resistors

- Enhanced CRC calculation unit

- 17 Timers

- 10 x 16-bit timers, each with up to 4 input

- capture/output compare/PWM or pulse counter

- and quadrature (incremental) encoder input

- 2 x 16-bit, advanced motor control PWM timer with dead-time generation and emergency stop

- 2 watchdog timers (Independent and Window)

- SysTick timer 24-bit downcounter

- 2 x 16-bit base timers

- Up to 12 communication interface

- Up to 2 x I2C interfaces(support SMBus/PMBus)

- Up to 5(W55MH32L) / 3(W55MH32Q) x USARTs

- Up to 2 SPI interfaces, 1 multiplexed with I2S interface

- CAN interface(2.0B Active)

- USB 2.0 full-speed interface(Optional internal

- 1.5K pull-up resistor)

- SDIO interface(only W55MH32L)

- Hardware encryption algorithm unit

- Built-in hardware algorithm(DES、AES、SHA)

- Provide a complete high-performance algorithm library

- TRNG: generate sequence of true random numbers

- Four independent true random sources, which can be configured individually

- 128BIT random numbers can be generated at

- one time

- Optional digital post-processing function

- Attack detection

- SENSOR: voltage & temperature sensor alarm

VBAT and VDD voltage can be detected

- independently – Provide temperature detection sensor

- Optional reset or interrupt after alarm

- SRAM scrambling

- Support address and data scrambling

- One Time Programmable (OTP)

- Support 32 Byte

# Directory

| 1 | SPECIFIC | ATION                                                             |  |  |  |  |  |

|---|----------|-------------------------------------------------------------------|--|--|--|--|--|

| 1 | .1 Devi  | ice overview                                                      |  |  |  |  |  |

| 1 | .2 Intro | oduction                                                          |  |  |  |  |  |

|   | 1.2.1    | 32-bit Arm <sup>®</sup> Cortex <sup>®</sup> -M3 Core              |  |  |  |  |  |

|   | 1.2.2    | TCP/IP Offload Engine (TOE)                                       |  |  |  |  |  |

|   | 1.2.3    | Embedded Flash memory9                                            |  |  |  |  |  |

|   | 1.2.4    | Memory Protection Unit(MPU)10                                     |  |  |  |  |  |

|   | 1.2.5    | Embedded SRAM 10                                                  |  |  |  |  |  |

|   | 1.2.6    | CRC (cyclic redundancy check) calculation unit10                  |  |  |  |  |  |

|   | 1.2.7    | Nested vectored interrupt controller (NVIC)10                     |  |  |  |  |  |

|   | 1.2.8    | External interrupt/event controller (EXTI)11                      |  |  |  |  |  |

|   | 1.2.9    | Clocks and startup11                                              |  |  |  |  |  |

|   | 1.2.10   | Boot modes11                                                      |  |  |  |  |  |

|   | 1.2.11   | Power supply schemes                                              |  |  |  |  |  |

|   | 1.2.12   | Power supply supervisor                                           |  |  |  |  |  |

|   | 1.2.13   | Voltage regulator                                                 |  |  |  |  |  |

|   | 1.2.14   | Low-power modes                                                   |  |  |  |  |  |

|   | 1.2.15   | DMA                                                               |  |  |  |  |  |

|   | 1.2.16   | RTC (real-time clock) and backup registers13                      |  |  |  |  |  |

|   | 1.2.17   | Timers and watchdogs 1                                            |  |  |  |  |  |

|   | 1.2.18   | I2C bus                                                           |  |  |  |  |  |

|   | 1.2.19   | Universal synchronous/asynchronous receiver transmitter (USART)16 |  |  |  |  |  |

|   | 1.2.20   | Serial peripheral interface (SPI)16                               |  |  |  |  |  |

|   | 1.2.21   | Audio Interface (I2S)                                             |  |  |  |  |  |

|   | 1.2.22   | SDIO                                                              |  |  |  |  |  |

|   | 1.2.23   | Controller area network (CAN)                                     |  |  |  |  |  |

|   | 1.2.24   | Universal serial bus (USB)                                        |  |  |  |  |  |

|   | 1.2.25   | General-purpose inputs/outputs(GPIO)                              |  |  |  |  |  |

|   | 1.2.26   | Analog-to-digital converter(ADC)                                  |  |  |  |  |  |

|   | 1.2.27   | Digital-to-analog converter(DAC)                                  |  |  |  |  |  |

|   | 1.2.28   | Temperature sensor                                                |  |  |  |  |  |

|   | 1.2.29   | Serial wire JTAG debug port(SWJ-DP)18                             |  |  |  |  |  |

|   | 1.2.30   | Embedded Tracking Module(ETM)19                                   |  |  |  |  |  |

|   | 1.2.31   | True random number generator(TRNG)19                              |  |  |  |  |  |

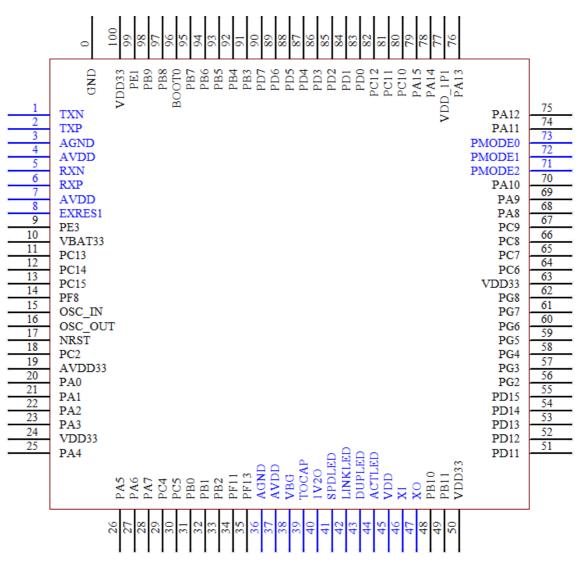

| 2 | PINOUTS  | AND PIN DESCRIPTION                                               |  |  |  |  |  |

|   | 2.1  | W55MH32L                                               |

|---|------|--------------------------------------------------------|

|   | 2.2  | W55MH32Q23                                             |

| 3 | ELE  | CTRICAL CHARACTERISTICS                                |

|   | 3.1  | Minimum and maximum values                             |

|   | 3.2  | Typical values                                         |

|   | 3.3  | Typical curves                                         |

|   | 3.4  | General operating conditions28                         |

|   | 3.5  | Operating conditions at power-up / power-down          |

|   | 3.6  | Embedded reset and power control block characteristics |

|   | 3.7  | Embedded reference voltage                             |

|   | 3.8  | Supply current characteristics                         |

|   | 3.9  | External clock source characteristics                  |

|   | 3.10 | Internal clock source characteristics                  |

|   | 3.11 | Crystal Characteristics of Ethernet                    |

|   | 3.12 | Wakeup time from low-power mode                        |

|   | 3.13 | PLL characteristics                                    |

|   | 3.14 | Memory characteristics                                 |

|   | 3.15 | Absolute maximum ratings (electrical sensitivity)      |

|   | 3.16 | I/O port characteristics                               |

|   | 3.17 | NRST pin characteristics                               |

|   | 3.18 | TIM timer characteristics                              |

|   | 3.19 | CAN (controller area network) interface                |

|   | 3.20 | 12-bit ADC characteristics                             |

|   | 3.21 | DAC electrical parameters                              |

|   | 3.22 | Temperature sensor characteristics                     |

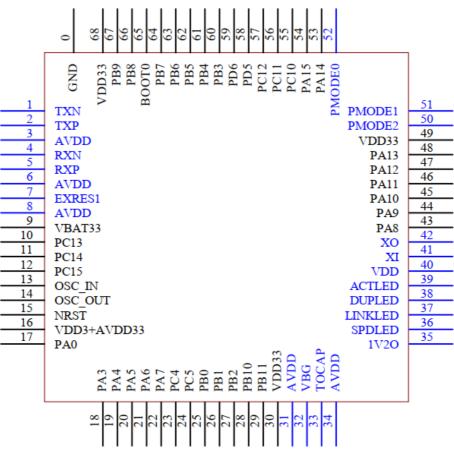

| 4 | PAC  | KAGE INFORMATION42                                     |

| 5 | DOC  | UMENT HISTORY INFORMATION                              |

# List of illustrations

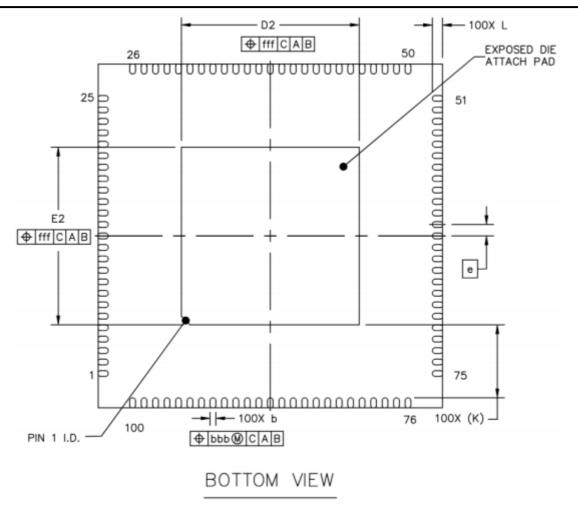

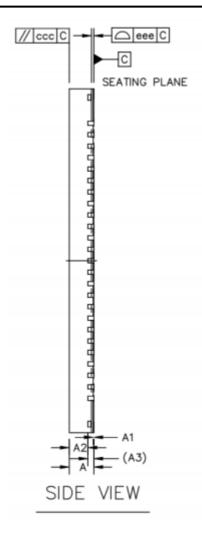

| Figure 1 W55MH32L package | 20 |

|---------------------------|----|

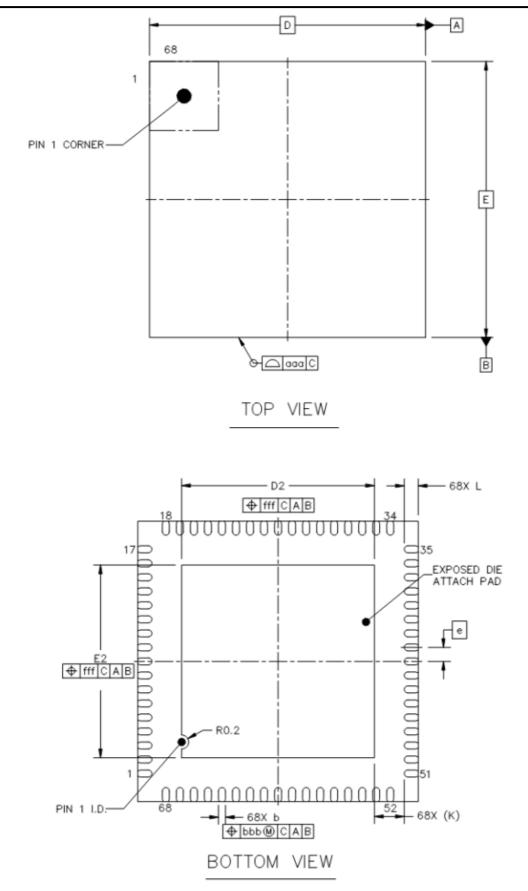

| Figure 2 W55MH32Q package | 23 |

| Figure 3 W55MH32L pack    | 44 |

| Figure 4 W55MH32Q pack    | 46 |

# List lists

| Figure 1 W55MH32L package |    |

|---------------------------|----|

| Figure 2 W55MH32Q package | 23 |

| Figure 3 W55MH32L pack    |    |

| Figure 4 W55MH32Q pack    |    |

# Introduction

This datasheet includes: the basic configuration of W55MH32(such as the capacity of built-in Flash and RAM, the type and quantity of peripheral modules, etc.), the number and assignment of pins, electrical characteristics, package information, etc.

# 1 Specification

## 1.1 Device overview

Table 1 Device Function Configuration Table

| F              | amily                   | W55MH32L      | W55MH32Q      |

|----------------|-------------------------|---------------|---------------|

| Flas           | h(Kbytes)               | 1024          | 1024          |

| SRAM           | M(Kbytes)               | 96            | 96            |

|                | Advanced                | 2             | 2             |

| Timers         | General-purpose         | 10            | 10            |

|                | Basic                   | 2             | 2             |

|                | SPI                     | 2             | 2             |

|                | 12C                     | 2             | 2             |

|                | USART/UART              | 5             | 3             |

| Communication  | USB                     | 1             | 1             |

|                | CAN                     | 1             | 1             |

|                | SDIO                    | 1             | -             |

|                | Ethernet                | 1             | 1             |

| GP             | IO PORT                 | 66            | 36            |

|                | bit ADC<br>of channels) | 3(12channels) | 3(12channels) |

|                | bit DAC<br>of channels) | 2(2channels)  | 2(2channels)  |

| True Randon    | n Number Module         | Support       | Support       |

| Hardware Encry | ption Algorithm Unit    | Support       | Support       |

| Page si        | ize (Kbytes)            | 4             | 4             |

| CPU            | frequency               | 216M          | 216M          |

| Operat         | ting voltage            | 2.0~3.6V      | 2.0~3.6V      |

| Operating      | g temperature           | -40 to +85°C  | -40 to +85°C  |

## 1.2 Introduction

## 1.2.1 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M3 Core

The 32-bit Arm® Cortex®-M3 core provides a cost-effective platform for meeting MCU requirements by reducing pin count and lowering system power consumption, while delivering exceptional computational performance and advanced interrupt system responsiveness.

## 1.2.2 TCP/IP Offload Engine (TOE)

#### **Brief introduction**

The TCP/IP Offload Engine (TOE) is an embedded all-hardware TCP/IP Ethernet controller, which can provide a more concise embedded network access solution. TOE technology enables users to use the hardware TCP/IP protocol stack to implement network access applications.

WIZnet all-hardware TCP/IP stack solution has been proven in many applications for many years, supporting TCP, UDP, IPv4, ICMP, ARP, IGMP and PPPoE protocols. The TOE embeds 32KB of internal cache for Ethernet packet processing.

The application of TOE technology allows users to implement Ethernet applications with some simple socket programming. Compared to other Ethernet solutions, this solution is faster and easier. Eight independent hardware socket can be used independently. At the same time, the TOE provides a WOL (Wake on LAN) function to reduce system power consumption.

#### Features

- Support full hardware TCP/IP protocols: TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE

- Support 8 independent ports (Socket) simultaneous communication

- Support power-down mode

- Wake on LAN support

- Independent 32K byte transceiver cache

- 10BaseT/100BaseTX Ethernet PHY

- Support auto-negotiation

#### 1.2.3 Embedded Flash memory

Embedded Flash is available for storing programs and data.

Table 2 Supply voltage and Flash Delay level matching table

| Flash Delay Level | HCLK(MHz)         |                   |  |  |  |  |

|-------------------|-------------------|-------------------|--|--|--|--|

|                   | Voltage Range     | Voltage Range     |  |  |  |  |

|                   | 2.3V - 3.6V       | 2.0V - 2.3V       |  |  |  |  |

| 0                 | 0 < HCLK <= 108   | 0 < HCLK <= 32    |  |  |  |  |

| 1                 | 108 < HCLK <= 216 | 32 < HCLK <= 64   |  |  |  |  |

| 2                 | -                 | 64 < HCLK <= 128  |  |  |  |  |

| 3                 | -                 | 128 < HCLK <= 192 |  |  |  |  |

| 4                 | -                 | 192 < HCLK <= 216 |  |  |  |  |

## 1.2.4 Memory Protection Unit(MPU)

The Memory Protection Unit (MPU) manages CPU access to memory, preventing one task from accidentally corrupting memory or resources used by another active task. This memory area is organized into up to 8 protected areas, which can in turn be subdivided into up to 8 sub-areas. The protected area size can range from 32 bytes to the entire 4 Gbytes of addressable memory.

MPUs are especially useful in applications where some critical or certified code must be protected from misbehavior by other tasks. It is usually managed by RTOS (Real Time Operating System). If a program accesses a memory location that is restricted by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the settings of the MPU area based on the executing process.

#### 1.2.5 Embedded SRAM

Up to 96 KB of built-in SRAM, accessible by the CPU with zero wait states for read and write operations.

## 1.2.6 CRC (cyclic redundancy check) calculation unit

The CRC (Cyclic Redundancy Check) calculation unit uses a fixed polynomial generator (with multiple selectable modes and hardware data processing) to generate a CRC code from a 32-bit data word.

In various applications, CRC-based techniques are used to verify the integrity of data transmission or storage. Within the scope of the EN/IEC 60335-1 standard, it provides a means for detecting flash memory errors.

## 1.2.7 Nested vectored interrupt controller (NVIC)

#### 8 priority levels.

- •Closely coupled NVIC gives low-latency interrupt processing

- •Interrupt entry vector table address passed directly to the core

- •Closely coupled NVIC core interface

- •Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- •Support interrupt tail-chaining function

- Processor state automatically saved

- Interrupt entry restored on interrupt exit without additional instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 1.2.8 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 19 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period.

## 1.2.9 Clocks and startup

The system clock selection is performed at startup. Upon reset, the internal 8 MHz RC oscillator is chosen as the default CPU clock. Subsequently, an external 4-16 MHz clock with failure monitoring can be selected. If the external clock fails, it is isolated and the system automatically switches to the internal RC oscillator. If interrupts are enabled, the software can receive the corresponding interrupt. Similarly, comprehensive interrupt management for the PLL clock can be enabled when needed, such as when an indirectly utilized external oscillator fails.

Multiple prescalers are available to configure the frequencies of the AHB, high-speed APB (APB2), and low-speed APB (APB1) domains. The maximum frequency for AHB and high-speed APB is 216 MHz, while the maximum frequency for low-speed APB is 108 MHz.

#### 1.2.10 Boot modes

At startup, boot pins are used to select one of three boot options:

- •Boot from program flash memory

- •Boot from System Memory

- •Boot from embedded SRAM

The Bootloader is located in System Memory. It is used to reprogram the Flash memory by using USART1.

#### 1.2.11 Power supply schemes

- VDD: Power supply for I/O pins and internal voltage regulator.

- VSSA, VDDA: Provide power for analog part of ADC, reset module, RC oscillator and PLL. VDDA and VSSA must be connected to VDD and VSS, respectively.

- VBAT: Backup power supply for RTC, external clock 32 kHz oscillator and backup registers (through internal power switch) when VDD is turned off.

Note: Refer to the general operating conditions for each voltage range

#### 1.2.12 Power supply supervisor

W55MH32 integrates an internal Power-On Reset (POR) and Power-Down Reset (PDR) circuit, which remains active at all times to ensure system operates when the supply voltage exceeds 2V. If VDD drops below the preset threshold (VPOR/PDR), the device is forced into a reset state without requiring an external reset circuit.

Additionally, it features a programmable voltage detector (PVD) that monitors the VDD/VDDA supply and compares it with the threshold VPVD. If VDD falls below or rises above VPVD, an interrupt is triggered. The interrupt handler can issue a warning or switch the microcontroller into a safe mode. The PVD function must be enabled through software.

#### 1.2.13 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR mode is used for normal operation.

- LPR mode is used for the stop mode of CPU

- Power down mode is used for CPU standby mode: the regulator output is in a highimpedance state, power to the core circuits is cut off and the regulator enters a zeropower state (however, register and SRAM contents will be lost)

The regulator remains active after reset and is turned off in standby mode, entering a high-impedance output state.

#### 1.2.14 Low-power modes

• Sleep mode

In Sleep mode, only the CPU stops while all peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Stop mode

Stop mode achieves the lowest power consumption while preserving SRAM and register contents. In this mode, it cuts off the power supply to all internal 1.1V domains. Additionally, the PLL, HSI RC oscillator, and HSE crystal oscillator are disabled. The regulator can be set to either normal mode or low-power mode.

The microcontroller can be awakened from stop mode by any signal configured as an EXTI signal. These EXTI signals include one of the 16 external I/O pins, the PVD output, the RTC alarm, or a USB wake-up signal.

Standby mode

Standby mode achieves the lowest power consumption. The internal voltage regulator is turned off and cuts the power to all internal 1.1V domains. Additionally, the PLL, HSI RC oscillator, and HSE crystal oscillator are disabled. Upon entering standby mode, SRAM and register contents are lost, but backup register contents remain preserved and the standby circuitry remains operational.

Exit from standby mode can be triggered by an external reset signal on NRST, an IWDG reset, a rising edge on a WKUP pin or an RTC alarm timeout.

**Note:** When entering shutdown or standby mode, the RTC, IWDG, and their respective clocks remain active.

#### 1.2.15 DMA

Supports up to 12 general-purpose DMA channels (DMA1 with 7 channels, DMA2 with 5 channels) for managing data transfers between memory and memory, peripherals and memory, and memory and peripherals. The DMA controller supports circular buffer management, preventing interrupts when a transfer reaches the buffer's end.

Each channel has dedicated hardware DMA request logic and can also be triggered by software. The transfer length, source address, and destination address can all be configured independently via software.

DMA can be used with major peripherals, including SPI/I2S, I2C, USART, advanced/general-purpose/basic timers (TIMx), ADC, DAC, and SDIO.

#### 1.2.16 RTC (real-time clock) and backup registers

The RTC and backup registers are powered through a switch. When VDD is available, the switch selects VDD as the power source; otherwise, power is supplied from the VBAT pin. The backup registers (42 16-bit registers) can store up to 84 bytes of user application data when VDD is turned off. Neither the RTC nor the backup registers are affected by system or power reset sources, and they remain intact when waking up from standby mode.

The real-time clock (RTC) features a continuously running counter that, with appropriate software, provides calendar clock functionality. It also supports alarm interrupts and periodic interrupts. The RTC can be driven by a 32.768 kHz oscillator using an external crystal, an internal low-power RC oscillator, or a high-speed external clock divided by 128. The internal low-power RC oscillator has a typical frequency of 40 kHz. To compensate for natural crystal deviations, the RTC clock can be calibrated using a 512 Hz output signal.

The RTC includes a 32-bit programmable counter, allowing long-duration measurements using a compare register. A 20-bit prescaler is used for the time base clock. By default, when the clock is set to 32.768 kHz, it generates a one-second time reference.

## 1.2.17 Timers and watchdogs

W55MH32series include at most 2 advanced-control timers, 10 general-purpose timers, 2 basic timers, 2 watchdog timers and 1 SysTick timer.

Following table compares the features of the advanced-control, general-purpose and basic timers.

| Timer         | Counter    | Counter | Prescaler     | Generate a  | Capture/Compare |         |  |

|---------------|------------|---------|---------------|-------------|-----------------|---------|--|

|               | Resolution | Туре    | Factor        | DMA Request | Channels        | Outputs |  |

| TIM1          |            | Up,     | Any integer   |             |                 |         |  |

| TIM8          | 16-bit     | down,   | between 1     | Yes         | 4               | Yes     |  |

|               |            | up/down | and 65536     |             |                 |         |  |

| TIM2          |            | Up,     | Any integer   |             |                 |         |  |

| TIM3          |            | down,   | between 1     |             |                 |         |  |

| TIM4          | 16-bit     | ,       |               | Yes         | 4               | No      |  |

| TIM5          |            | up/down | and 65536     |             |                 |         |  |

| <b>T</b> 1140 |            |         | Any integer   |             |                 |         |  |

| TIM9          | 16-bit     | Up      | between 1 and | No          | 2               | No      |  |

| TIM12         |            |         | 65536         |             |                 |         |  |

| TIM10         |            |         | Any integer   |             |                 |         |  |

| TIM11         |            |         | between 1     |             | 1               | No      |  |

| TIM13         | 16-bit     | Up      | and 65536     | No          |                 |         |  |

| TIM14         |            |         | and 05550     |             |                 |         |  |

|               |            |         | Any integer   |             |                 |         |  |

| TIM6          | 16-bit     | Up      | between 1 and | Yes         | 0               | No      |  |

| TIM7          |            |         | 65536         |             |                 |         |  |

Table 3 TIM configuration table

#### Advanced-control timer (TIM1 and TIM8)

The two advanced control timers (TIM1 and TIM8) can be regarded as three-phase PWM generators with six channels. They feature complementary PWM outputs with deadtime insertion and it can function as fully capable general-purpose timers.

The 4 independent channels can be used for

- Input capture

- Output comparison

- PWM generator (edge- or center-aligned modes)

- Signal pulse output

When configured as a general-purpose 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

In debug mode, the counters can be frozen, and PWM outputs are disabled, effectively shutting off switches controlled by these outputs. Many features are identical to standard TIM timers, and they share the same internal structure. As a result, advanced control timers can operate in conjunction with TIM timers through the timer linkage function, enabling synchronization or event linking.

#### General-purpose timer(TIM2、TIM3、TIM4、TIM5)

There are up to four synchronizable general-purpose timers embedded in the W55MH32 devices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler and 4 independent channels each for input capture/output compare, PWM or single-pulse mode output. The general-purpose timers can work together with the advanced-control timer via the Timer Link feature for synchronization or chaining events. These counters can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs. They all have independent DMA request generation.

These timers are also capable of processing incremental encoder signals as well as digital outputs from 1 to 3 hall-effect sensors.

#### General-purpose timer(TIM10、TIM11、TIM9)

These timers are based on a 16-bit auto-reload counter and a 16-bit prescaler. TIM10 and TIM11 have one independent channel, while TIM9 has two independent channel outputs for input capture/output comparison, PWM or single-pulse output. They can fully synchronize general purpose timers with TIM2, TIM3, TIM4, TIM5. They can also be used as a simple time base.

#### General-purpose timer(TIM13、TIM14、TIM12)

These timers are based on a 16-bit auto-reload counter and a 16-bit prescaler. TIM13 and TIM14 have one independent channel, while TIM12 has two independent channels outputs for input capture/output comparison, PWM or single-pulse output. They can fully synchronize general purpose timers with TIM2, TIM3, TIM4, TIM5. They can also be used as a simple time base.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40kHz internal RC. As it operates independently with the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the system when a problem occurs, or as a free-running timer for application timeout management. The watchdog can be configured to start via software or hardware through option bytes. The counter can be frozen in debug mode.

#### Basic timer TIM6 and TIM7

These timers are mainly used for the generating of DAC triggers. They can also be used as a universal 16-bit time base.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the system when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### SysTick timer

This timer is dedicated for OS, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source

#### 1.2.18 I2C bus

Up to two I2C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes. The I2C interface supports 7-bit or 10-bit addressing, and the 7-bit slave mode supports dual-slave addressing. A hardware CRC generation /verification is embedded.

They can be served by DMA and they support SM Bus 2.0/PM Bus.

# 1.2.19 Universal synchronous/asynchronous receiver transmitter (USART)

Three universal synchronous/asynchronous receiver transmitter(USART1, USART2 and USART3) and two universal asynchronous receiver transmitter(UART4 and UART5). The five interfaces provide asynchronous communication, IrDA SIR ENDEC support, Multi-processor communication mode, single-line semi-duplex communication mode and LIN Master/Slave capability.

USART1 interface communication rate can reach 13.5Mbits/s.

USART1, USART2 and USART3 provide hardware management of the CTS and RTS signals, are compliant with ISO7816 smart card mode and SPI-like communication mode.

## 1.2.20 Serial peripheral interface (SPI)

Up to 2 SPI interfaces. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

All SPIs can be served by the DMA controller.

### 1.2.21 Audio Interface (I2S)

A standard I2S interface (multiplexed with SPI3) can operate in either master or slave mode. This interface supports 16-bit or 32-bit data transmission and can be configured as either an input or output channel. It supports audio sampling frequencies ranging from 8 kHz to 48 kHz. When configured in master mode, the I2S interface can output a master clock at 256 times the sampling frequency to an external DAC or CODEC (decoder).

#### 1.2.22 SDIO

The SD/SDIO/MMC host interface can support 3 different data bus modes in the MMC Card System Specification 4.2: 1-bit (default), 4-bit, and 8-bit. SDIO Memory Card Specification 2.0 supports two data bus modes: 1-bit (default) and 4-digit. The current chip version can only support one SD/SDIO/MMC version 4.2 card at a time but can simultaneously support multiple MMC version 4.1 or early version cards.

In In addition to SD/SDIO/MMC, this interface is fully compatible with the CE-ATA digital protocol version 1.1.

#### 1.2.23 Controller area network (CAN)

The CAN interface supports protocol of 2.0A and 2.0B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifier as well as extended frames with 29-bit identifier. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

#### 1.2.24 Universal serial bus (USB)

Embedded a full-speed USB device controller, follows the full-speed USB device (12m/s) standard. The endpoint can be configured by software and includes standby/wakeup features. The USB dedicated 48MHz clock is directly generated by the internal master PLL (with a selectable clock source).

#### 1.2.25 General-purpose inputs/outputs (GPIO)

Each GPIO pin can be configured via software as an output (push-pull or open-drain), an input (with or without pull-up or pull-down), or as a multiplexed peripheral function. Most GPIO pins are shared with digital or analog peripheral functions. Except for ports with analog input functionality, all GPIO pins support high-current drive capability.

When necessary, the peripheral function of an I/O pin can be locked through a specific operation to prevent unintended writes to the I/O registers. Additionally, each I/O can be configured with internal pull-up or pull-down resistors, reducing the need for external resistors.

## 1.2.26 Analog-to-digital converter (ADC)

Supports up to three 12-bit Analog-to-Digital Converters (ADCs) with up to 12 external channels, capable of single or scan conversions. In scan mode, conversions are

automatically performed on a selected group of analog inputs.

Additional logic functions available on the ADC interface include:

- Synchronized sampling and hold

- Interleaved sampling and hold

- Single sampling

The ADC can operate with DMA for efficient data transfer.

The analog watchdog function enables highly precise monitoring of one, multiple, or all selected channels. If the monitored signal exceeds a predefined threshold, an interrupt is triggered.

Events generated by standard timers (TIMx) and advanced control timers (TIM1 and TIM8) can be internally cascaded to the ADC for start and injected triggers, allowing applications to synchronize AD conversions with the system clock.

## 1.2.27 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can convert two digital signals into two analog voltage outputs.

This dual digital interface supports the following features:

- Two DAC converters, each with a dedicated output channel

- 8-bit or 12-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update functionality

- Noise wave generation

- Triangle wave generation

- Independent or synchronized conversion of both DAC channels

- DMA functionality available for each channel

- External trigger for conversion

- Input reference voltage V\_REF+

The DAC channels can be triggered by the update output of a timer, which can also be connected to different DMA channels.

#### 1.2.28 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The temperature sensor is internally connected to the ADC11\_IN16 input channel which is used to convert the sensor output voltage into a digital value

#### 1.2.29 Serial wire JTAG debug port(SWJ-DP)

The embedded SWJ-DP interface combines JTAG and Serial Wire Debug (SWD), allowing connection via either the Serial Wire Debug interface or the JTAG interface. The JTAG TMS and TCK signals share pins with SWDIO and SWCLK, respectively. A specific signal sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

#### 1.2.30 Embedded Tracking Module (ETM)

Using the Embedded Trace Macrocell (ETM), a high-speed compressed data stream can be output from the CPU core through a minimal number of ETM pins to an external Trace Port Analyzer (TPA) device. This provides developers with clear insights into instruction execution and data flow.

The TPA device can connect to the debugging host via USB, Ethernet, or other highspeed channels. Real-time instruction and data flow can be recorded by debugging software on the host and displayed in the desired format. TPA hardware is available from development tool vendors and is compatible with third-party debugging software.

#### 1.2.31 True random number generator (TRNG)

The TRNG (True Random Number Generator) unit is used to generate a sequence of true random numbers. Each operation produces a 128-bit true random number sequence. It can be configured to generate a CPU interrupt request after random number generation.

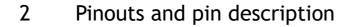

## 2.1 W55MH32L

Figure 1 W55MH32L package

#### Table 4 W55MH32L pin description

| NO | Pin Name           | Туре | I/O Level | Main<br>Function<br>(after reset) | Default/ Description                                                                                                                             | Remap |

|----|--------------------|------|-----------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1  | TXN                | AO   | -         | TXN                               | TXP/TXN Signal Pair                                                                                                                              | -     |

| 2  | TXP                | AO   | -         | ТХР                               | The differential data is transmitted to the media on<br>the TXP/TXN signal pair.                                                                 | -     |

| 3  | AGND               | AGND | -         | -                                 | Analog ground of ethernet                                                                                                                        | -     |

| 4  | AVDD               | PWR  | -         | -                                 | Analog 3.3V power of ethernet                                                                                                                    | -     |

| 5  | RXN                | Al   | -         | RXN                               | RXP/RXN Signal Pair                                                                                                                              | -     |

| 6  | RXP                | Al   | -         | RXP                               | The differential data from the media is received on<br>the RXP/RXN signal pair.                                                                  | -     |

| 7  | AVDD               | PWR  | -         | -                                 | Analog 3.3V power of ethernet                                                                                                                    | -     |

| 8  | EXRES              | -    | -         | -                                 | External Reference Resistor<br>It should be connected to an external resistor<br>(12.4KΩ, 1%) needed for biasing of internal analog<br>circuits. | -     |

| 9  | PE3                | -    | -         | -                                 | -                                                                                                                                                | -     |

| 10 | VBAT               | VBAT | S         | -                                 | VBAT                                                                                                                                             | -     |

| 11 | PC13-<br>TAMPERRTC | I/0  | -         | PC13                              | TAMPER-RTC                                                                                                                                       | -     |

| 12      OCCUM      VO      PC14      OCCUM      OCCUM        13      OCCUM      VO      PC14      OCCUM      Image: Construction of the second se                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | NO | Pin Name | Туре | I/O Level | Main<br>Function<br>(after reset) | Default/ Description                                                                                                                                                                                                                      | Remap     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------|------|-----------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 13      PPC15      OSC22_OUT         14      DOSE_2001      1/10      -      PFS      2062_316         15      DSC_10      1      OSC_00           16      OSC_10      -      OSC_00           16      OSC_100      -      OSC_00           17      MRSTT      1      -      REST          17      MST      -      REST          18      PC2      I/O      PAD      MC213_INT2_CTF         12      PAD      I/O      PAD      MC213_INT2_CTF         12      PAD      I/O      PAD      MC217_INT2_CTF         13      I/O      PAD      I/O/O      I/O/O         14      I/O      PAD      I/O/O/O/I/I/O/O          14      I/O      PAD      I/O/O/I/I/O/O/O/I/I/O/O/I/I/O/O/O/I/I/O/O/I/I/O/O/I/I/O/I/I/O/I/I/O/I/I/O/I/I/O/I/I/O/I/I/O/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12 |          | I/0  | -         | PC14                              | OSC32_IN                                                                                                                                                                                                                                  | -         |

| 14      000-8700      1/0      PF8      ACC 106        15      05C 007      0      05C 007      0      05C 007        16      05C 007      0      05C 007      0      05C 007        17      m8STT      1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13 | PC15-    | 1/0  | -         | PC15                              | OSC32 OUT                                                                                                                                                                                                                                 | _         |

| 15    05C, IN    1    .    05C, IN    .      17    mRESET    1    .    mRESET    .    .      18    PC2    VIO    PC2    ADC123, IN12    .    .      19    VIDDA    PWR    .    .    .    .    .      20    PA0 WKUP    VIO    .    PA0    .    .    .    .    .    .      21    PA1    VIO    .    PA1    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    . <td< td=""><td></td><td></td><td></td><td></td><td></td><td>_</td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |          |      |           |                                   | _                                                                                                                                                                                                                                         |           |

| 16      005: CUT      0      -      005: CUT      -        18      PC2      1/0      -      04521      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      -      - <td></td> <td></td> <td></td> <td></td> <td></td> <td>ADC3_IN0</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |          |      |           |                                   | ADC3_IN0                                                                                                                                                                                                                                  |           |

| 17      netSetT      1      -      netSetT        18      PC2      I/O      PC2      ADC123_M12      -        19      VDDA      PWR      -      -      WIP/D63712_TG7      -        20      PA0_WRUP      I/O      -      PA0_D01712_TG7      -      -        21      PA1      1/O      -      PA1      TWD_CATTING CTL      -        22      PA2      1/O      -      PA2      TWD_CATTING CTL      -        23      PA3      1/O      -      PA2      TWD_CATTING CTL      -        24      YOD      PWR      -      -      -      -        24      YOD      PA4      SM1_MSC/ADC2_LNM/      -      -        25      PA4      1/O      PA5      SM1_MSC/ADC2_LNM/      -      -        26      PA7      1/O      PA5      SM1_MSC/ADC2_LNM/      -      -        27      PA6      1/O      PA6      SM1_MSC/ADC2_LNM/      -      -        28      PA7      1/O </td <td></td> <td>_</td> <td></td> <td></td> <td>_</td> <td>-</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | _        |      |           | _                                 | -                                                                                                                                                                                                                                         |           |

| Ha      PC2      MOD      PC2      ACC12 IN12         19      VDD      PA0      WICP POSAT2 C57          20      PA0 WKUP      1/0      PA1      USAT2 C57          21      PA1      1/0      PA1      USAT2 FX/AC12 IN17          21      PA1      1/0      PA2      USAT2 FX/AC12 IN17          22      PA2      1/0      PA3      USAT2 FX/AC12 IN17          23      PA3      1/0      PA3      TXX_CHT2 IN17          24      VD0      PWR             25      PA4      1/0      PA3      S911 SC/L2 IN17          26      PA5      1/0      PA5      S911 SC/L2 IN17          27      PA6      1/0      PA7      TML_2 C11      TML_2 C11         28      PA7      1/0      PA7      TML_2 C11 <t< td=""><td></td><td>_</td><td>-</td><td></td><td>_</td><td>_</td><td>-</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | _        | -    |           | _                                 | _                                                                                                                                                                                                                                         | -         |

| 20      PAD_WRUP      I/O      PAD      WKIP PUSATE_CTS/<br>ACCE2 NOTMAC_CH_ETR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTRUE_TR/<br>TWS_CHTTR | 18 |          | 1/0  | -         |                                   | ADC123_IN12                                                                                                                                                                                                                               | -         |

| 20      PA/MKUP      // 0      -      PA0      ACC121 NOTWL_CH1 TEK/<br>INC_CH17106_CH17      -        21      PA1      // 0      -      PA1      UGAD_CH17106_CH17      -        22      PA2      // 0      -      PA2      TWA_CH17106_CH17      -        23      PA3      // 0      -      PA1      UK_CH17106_CH17      -        24      V00      PWR      -      -      -      -        25      PA4      // 0      -      PA4      DACCT17405_CH4      -        25      PA4      // 0      -      PA4      DACCT1405_CH4      -        26      PA5      // 0      -      PA4      DACCT24      -        27      PA6      // 0      -      PA4      DACCT247      -        27      PA5      // 0      -      PA5      DACCT247      -      -        28      PA7      // 0      -      PA5      DACCT247      TMACACT14704      TMACT47104        29      PC4      // 0      -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19 | VDDA     | PWR  | -         | -                                 | -                                                                                                                                                                                                                                         | -         |

| L1      PA1      TW0 C1:27TWS C12      -        22      PA2      1/0      -      PA2      TWA2_C117TWS C12      -        23      PA3      1/0      -      PA3      TWA2_C117TWS C12      -        24      VDD      PVR      -      -      -      -        24      VDD      PVR      -      -      -      -        25      PA4      1/0      -      PA4      DWA2_C117TWS C12      -        26      PA5      1/0      -      PA4      DWA2_C127TWS C12      -        27      PA6      1/0      -      PA4      DWA2_C127WS      -        28      PA7      1/0      -      PA4      DWA2_C127WS      TWA3_C147TWS      TWA3_C147TWS        28      PA7      1/0      -      PA7      TWA3_C147TWS      TWA3_C147TWS      TWA1_C147WS        28      PA7      1/0      -      PA7      TWA3_C147TWS      TWA1_C147WS        29      PC4      1/0      -      PC5      AOC1_WR7 TWA3_C147W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20 | PA0-WKUP | 1/0  | -         | PA0                               | ADC123_IN0/TIM2_CH1_ETR/                                                                                                                                                                                                                  | -         |

| 22      PA2      I/O      PA2      USATT2_TXACT21_N2/<br>TW2_CH17MS_CH2/        23      PA3      I/O      PA3      TW2_CH17MS_CH1/M2        24      VOD      PVR      -      -        25      PA4      I/O      PA4      SP11_NS/LSATT2_CK1/        26      PA4      I/O      PA4      SP11_NS/LSATT2_CK1/        27      PA4      I/O      PA4      SP11_NS/LSATT2_CK1/        28      PA4      I/O      PA4      SP11_NS/LSATT2_CK1/        29      PA4      I/O      PA5      SP11_NS/LSATT2_NA/        20      PC4      I/O      PA6      TW3_CH17_NM_SRIN/      TM41_SRIN        21      PA6      I/O      PA6      SP11_NS/LSATT2_NM/      TM41_SRIN        28      PA7      I/O      PA7      SP11_NS/LSATT2_NM/      TM1_SCH1/M1        28      PA7      I/O      PA6      SP11_NS/LSATT2_NM/      TM1_SCH1/M1        29      PE1      I/O      PR1      ASCT2_NP1/M3_CH1/M1      TM1_SCH1/M1        29      PPC4      I/O      PR1      PR1_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21 | PA1      | 1/0  | -         | PA1                               | USART2_RTS/ADC123_IN1/                                                                                                                                                                                                                    | -         |

| 23      PA3      I/0      -      PA3      TM2_CH4TUBS_CH4/      -        24      V00      PWR      -      SP1_MS_USART_SG/      -      -        25      PA4      I/0      -      PA4      DDC_STUSART_SG/      -      -        26      PA5      I/0      -      PA5      SP1_MS0/ADC12_NG/      -      -        27      PA6      I/0      -      PA6      TM3_CH1TUB_KRM/      TIM1_BIN        28      PA7      I/0      -      PA6      TM3_CH1TUB_KRM/      TIM1_CH1N        28      PA7      I/0      -      PA7      TM3_CH1TUB_KRM/      TIM1_CH1N        28      PA7      I/0      -      PC5      AOC12_NH1      -      -        30      PC5      I/0      -      PC5      AOC12_NH1      -      -      -        31      PB0      I/0      PB1      AC12_NH7TM3_CH4/      TIM1_CH2N      TIM1_CH2N        32      PB1      I/0      FT      PF1      -      -      -      -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22 | PA2      | 1/0  | -         | PA2                               | USART2_TX/ADC123_IN2/<br>TIM2_CH3/TIM5_CH3/                                                                                                                                                                                               | -         |

| 25      PA4      I/O      -      PA4      SPI_INS/USART2_CK/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23 | PA3      | 1/0  | -         | PA3                               | TIM2_CH4/TIM5_CH4/                                                                                                                                                                                                                        | -         |

| 25      PAA      DVO      PAA      DAC_OUTI ADC12_INA        26      PAS      I/O      PAS      DAC_OUTI         27      PA6      I/O      PAS      DAC_OUTI         27      PA6      I/O      PAS      DAC_OUTI         28      PA7      I/O      PA6      TRBL_CHTING, BON/      TMI_DECLINFT        28      PA7      I/O      PA7      PA6      TRBL_CHTING, BON/      TMI_DECLINFT        29      PC4      I/O      PA7      TRBL_CHTING, CHIN/      TUNI_CHIN        20      PC5      I/O      PC4      ADC12_INFT         30      PC5      I/O      PC4      ADC12_INFT         31      PB0      I/O      PE8      ADC12_INFT         32      PB1      I/O      FP      PE1/DEOTI          32      PB1      I/O      FT      PE11           34      PF13      I/O      FT      PE11     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24 | VDD      | PWR  | -         | -                                 | -                                                                                                                                                                                                                                         |           |